近日,一則美國制造出0.7納米芯片的芯片在筆者的朋友圈傳播。與此同時傳播的新還有類似繞開EUV光刻機、美國打造全球分辨率最高光刻系統。這究竟是個什麼新聞?從現階段看EUV光刻機會是怎樣的一個未來?讓我們來還原以下這個新聞本身。

美國企業推出0.7nm芯片?

這其實是來自美國Zyvex Labs的一個報道。

在9月21日, Zyvex Labs宣佈,推出世界上最高分辨率的光刻系統 — ZyvexLitho1。該工具使用量子物理技術來實現原子精度圖案化和亞納米(768 皮米——Si (100) 2 x 1 二聚體行的寬度)分辨率。這一進步使量子計算機能夠為真正安全的通信提供牢不可破的加密;還更快的藥物發現和更準確的天氣預報。

報道進一步指出,ZyvexLitho1 是一款基於掃描隧道顯微鏡 (STM:Scanning Tunneling Microscopy) 儀器,Zyvex Labs 自 2007 年以來一直在改進該儀器。ZyvexLitho1 包含許多商業掃描隧道顯微鏡所不具備的自動化特性和功能。

“構建可擴展的量子計算機存在許多挑戰。我們堅信,要實現量子計算的全部潛力,需要高精度制造,”Michelle Simmons 教授說。“我們對 ZyvexLitho1 感到興奮,這是第一個提供原子精度圖案化的商用工具。”

STM 光刻技術的發明者 Joe Lyding 教授表示:“迄今為止,Zyvex Labs 技術是這種原子級精確光刻技術的最先進和唯一的商業化實現。” Lyding 是 2014 年費曼獎獲得者,也是伊利諾伊大學電氣與計算機工程專業的 Robert C. MacClinchie 特聘教授。

ZyvexLitho1 中嵌入的是我們的 ZyVector。這種具有低噪聲和低延遲的 20 位數字控制系統使我們的用戶能夠為固態量子器件和其他納米器件和材料制作原子級精確的圖案。完整的 ZyvexLitho1 系統還包括配置用於制造量子器件的 ScientaOmicron 超高真空 STM。

“我期待繼續與 Zyvex 進行富有成效的合作,”ScientaOmicron 產品經理 SPM Andreas Bettac 博士評論道。“在這裡,我們將最新的 UHV 系統設計和 ScientaOmicron 久經考驗且成熟的 SPM 與 Zyvex 用於基於 STM 的光刻的專用高精度 STM 控制器相結合。”

從報道可以看到,該產品還得到美國DARPA(國防高級研究計劃署)、陸軍研究辦公室、能源部先進制造辦公室和德克薩斯大學達拉斯分校的 Reza Moheimani 教授的支持,後者最近獲得工業成就獎國際自動控制聯合會授予“支持在單原子尺度上制造量子矽器件的控制發展”獎。

由此可見,這個所謂的0.7nm芯片,可能我傳統意義上的芯片制造工藝是不一樣的。

對半導體行業有解的讀者應該清楚,我們平時所謂的多少納米,其實是一個工藝節點的代號。通常意義上,這個代號是用一個數字命名,後跟納米的縮寫,例如7nm、5nm、3nm 等。

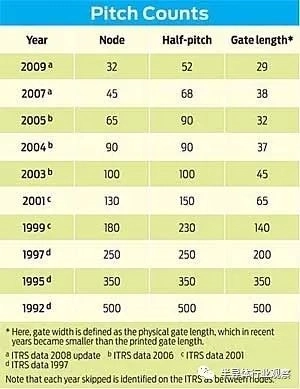

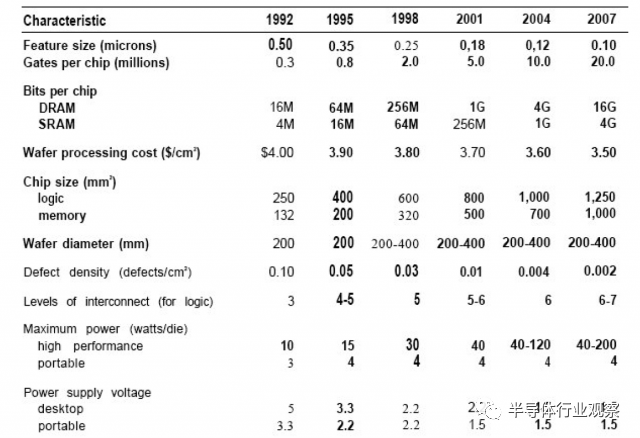

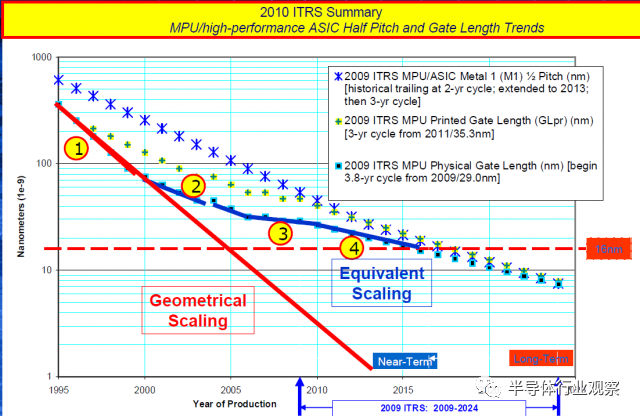

從大約 1960 年代到 1990 年代末,節點是根據它們的門長度命名的。這張來自 IEEE 的圖表顯示這種關系。

半導體制造涉及巨大的資本支出和大量的長期研究。從論文中引入新技術方法到大規模商業制造之間的平均時間長度約為 10-15 年。幾十年前,半導體行業認識到,如果存在用於節點引入的通用路線圖以及這些節點將針對的特征大小,這將對每個人都有好處。

這將允許廣泛、同時開發將新節點推向市場所需的所有難題。多年來,ITRS(國際半導體技術路線圖)發佈該行業的總體路線圖(已經停止更新)。這些路線圖跨越 15 年,為半導體市場設定總體目標。

長期以來,柵極長度(晶體管柵極的長度)和半間距(芯片上兩個相同特征之間距離的一半)與工藝節點名稱相匹配,但上一次出現這種情況是在1997 年。pitch 繼續匹配節點名稱幾代,但在任何實際意義上不再與它相關。

由此可見,這在工藝上與我們熟悉的工藝節點是不太一樣。至於這個光刻,則是所謂的STM光刻。

繞開EUV光刻技術?

從相關報道指出,達成這個0.7納米分辨率的光刻系統這是一種稱為氫去鈍化光刻(Hydrogen Depassivation Lithography )的技術,它是一種電子束光刻技術 (EBL),可實現原子分辨率。

據維基百科介紹,電子束光刻(通常縮寫EBL)是掃描聚焦電子束以在覆蓋有稱為光刻膠(曝光)的電子敏感膜的表面上繪制自定義形狀的做法。電子束改變光刻膠的溶解度,通過將抗蝕劑浸入溶劑中(顯影),可以選擇性地去除曝光或未曝光區域。與光刻一樣,其目的是在抗蝕劑中創建非常小的結構,然後通常通過蝕刻將其轉移到基板材料上。

電子束光刻的主要優點是它可以繪制具有sub-10 nm 分辨率的自定義圖案(直接寫入) 。這種形式的無掩模光刻具有高分辨率和低產量,限制其用於光掩模制造、半導體器件的小批量生產以及研發。

據介紹,該機器的用途包括為基於量子點的量子比特制作極其精確的結構,以實現最高的量子比特質量。該產品可用於其他非量子相關應用,例如構建用於生物醫學和其他化學分離技術的納米孔膜。

如上所述,該產品的缺點是吞吐量非常低,換而言之,它可能適合制造小批量的量子處理器芯片,對於大批量消費電子產品來說,這不是一個好的解決方案。

Zyvex Labs在官網中也表示,該系統能夠使原子精密光刻成為現實,當中用於 STM 光刻的 UHV 系統 、前體氣體計量和 Si MBE 、數字矢量光刻和自動化和腳本。他

們表示,如果沒有亞納米分辨率和精度,這種 7.7 納米(10 像素)正方形的曝光是不可能的。

Zyvex Labs指出,ZyvexLitho1 使用氫去鈍化光刻從 Si (100) 2×1 重建表面去除 H 原子。這種自我顯影的曝光技術本質上是二元的。H-Si 鍵要麼斷裂(將 H 原子送入真空),要麼沒有。沒有部分暴露或鄰近效應。

利用這個過程和作為矽表面晶格的全局基準網格允許數字光刻。亞納米像素是 4 個表面矽原子。

可以將設計網格與我們的像素網格相同的計算機輔助設計 (CAD) 文件加載到 ZyvexLitho1 中,並且可以自動將圖案分割成不同的幾何形狀,從而允許尖端矢量與不同的光刻模式一起使用。然後可以自動進行曝光。

他們還強調,由於光刻模式和成像模式在能量上分離良好,因此可以在光刻前後對Si表面進行成像。這種非曝光成像模式允許自動識別矽晶格,因此可以自動識別像素在表面上的位置。這種 Lattice Lock 過程自動保持尖端定位(以及因此光刻)準確。

從他們提供的表格上看,該系統擁有以下特點:

那麼,關於這個的討論又來到——EBL能取代傳統光刻嗎?

EBL能成為新選擇嗎?

所謂光刻,是芯片制造中的一種圖案化工藝。該過程涉及將圖案從光掩模轉移到基板。這主要是使用配備有光學光源的步進器和掃描儀來完成的,這也是我們現在主流的芯片制造方式,大傢熟悉的EUV和DUV就是使用這種方式的。

其他形式的光刻包括直寫電子束(direct-write e-beam)和納米壓印( nanoimprint)。在研發中還有幾種下一代光刻(NGL)技術——如多光束電子束和定向自組裝(DSA)。

據美國NIST方面介紹,電子束光刻允許精細控制納米結構特征,這些特征構成多種器件技術的基礎。讓10 nm 的橫向分辨率、1 nm 的放置精度和 1 mm 的圖案化區域都是可能的。

然而,實現這些性能指標取決於許多特定於樣品的相互依賴的因素——圖案定義和斷裂、基板和掩模材料、曝光前和曝光後工藝、對準特征定義——以及關鍵的細節光刻系統的操作。

NIST表示,作為一項核心能力,其開發的工藝處於或接近傳統電子束光刻技術的極限,以推進各個領域的納米級設備和測量科學。

例如:用於精確計時的芯片級頻率梳;用於波長和量子頻率轉換的非線性集成光學;用於傳感、轉換和非線性動力學研究的片上腔光機械和微/納米機電系統;具有用於量子信息的非線性和量子發射器光源的量子光子集成電路;從紫外到紅外的超表面,用於捕獲和探測原子和離子、偏振測量、成像和時空超快激光脈沖整形;用於像差校正的光學顯微鏡標準。

但正如很多報道中所說,其吞吐和準確度,限制EBL的發展。根據eBeam Initiative的一份調查顯示,使用類似電子書光刻這樣的直寫設備制作一份掩膜寫入時間大概在2.5到13個小時不等,其平均數在6.8個小時。根據該組織的報告,對於復雜掩膜而言,最長寫入時間在14到60個小時。

一般來說,制造商們對於寫入時間超過24個小時的掩膜設計方案會比較頭疼。因為過長的寫入時間就意味著更高的成本,更長的處理時間和良率問題。