近期,2nm等先進芯片發展備受行業關註。6月17日臺積電舉行的技術論壇上,晶圓代工龍頭臺積電(TSMC)首次披露,到2024年,臺積電將擁有阿斯麥(ASML)最先進的高數值孔徑極紫外(high-NAEUV)光刻機,用於生產納米片晶體管(GAAFET)架構的2nm(N2)芯片,預計在2025年量產。

與此同時,6月初被美國總統拜登亞洲行接見後,緊接著,韓國三星電子副會長李在鎔又馬不停蹄奔赴歐洲,有報道指三星電子在阿斯麥獲得瞭十多臺EUV光刻機,並於本周起大規模生產3nm芯片,而2nm將於2025年量產。

盡管量產2nm芯片依然還需時日,但此時此刻,臺積電、三星電子兩傢芯片大廠不約而同的尋求下一代EUV光刻機,意味著現在“2nm技術戰”已經打響。

“到瞭未來的技術節點,間距微縮將減緩,矽晶體管似乎隻能安全地微縮至2nm,而在那之後,我們可能就會開始使用石墨烯。”芯片制造的核心軟件EDA巨頭新思科技(Synopsys)研究專傢Victor Moroz的這句話道出瞭2nm技術的重要性:2nm是矽芯片的最後一戰。

砸下600億美元奪nm

1965年,英特爾創始人戈登·摩爾提出瞭大名鼎鼎的“摩爾定律”(Moore's law)理論,即集成電路上可容納的晶體管數目,約每隔兩年便會增加一倍。

自此之後,“摩爾定律”一直驅動著集成電路和芯片產業的飛速發展。過去的50年中,芯片裡的晶體管密度和芯片的性能,都呈現瞭指數級的增長,而使用晶體管進行計算的成本和功耗也呈現瞭指數級的下降。可以說,“摩爾定律”是驅動芯片半導體產業,甚至整個社會在這半個世紀裡飛速前進的根本動力。

但隨著芯片制程進入到5nm、3nm,很多工藝結構的設計已經開始接近於原子層面,對設計的精度、良率都有很高的要求,也使得技術的突破變得愈加困難。因此,如今的芯片微縮,則更加依賴光刻機技術以及新的架構設計的演進方法。

當前,全球具備5nm及以下制程芯片制造實力的晶圓制造企業,隻有臺積電和三星電子兩傢。而他們卻正在展開一場投資超600億美元、以納米乃至原子厚度為目標的先進制程競賽。

競賽開始,先進技術的資本投入至關重要。

根據兩傢公司財報顯示,2021年,臺積電資本支出達300億美元,而今年預計資本支出將達400-440億美元,其中近90%用於先進制程以及特殊工藝技術;三星電子2021年則在半導體領域投資約337億美元,並預計未來五年投資3600億美元,主要用於半導體先進制程等。

四大核心技術競爭

當投入百億,甚至是千億美元,如今這場“2nm技術戰”中,臺積電和三星電子兩傢公司分別在晶體管結構、光刻、材料、封裝等進行核心技術創新競爭。

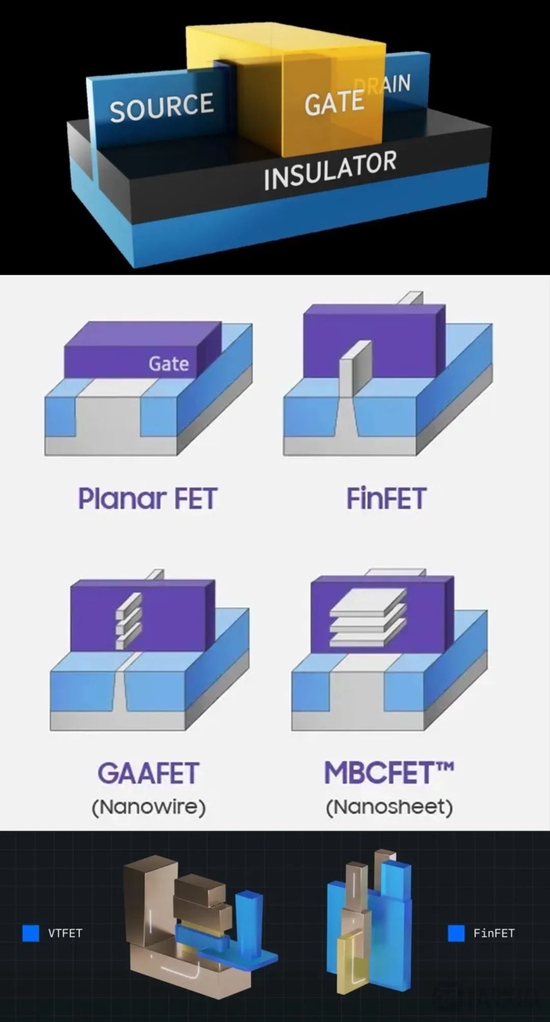

首先是新的晶體管結構。

臺積電2nm采用納米片晶體管(GAAFET)結構,相比目前5nm鰭式場效應晶體管(FinFET)架構,GAAFET能更好控制漏電,且性能提升10%-15%,功耗卻降低25%-30%。

實際上,芯片內部的場效應晶體管,分別包括源極(Source)、漏極(Drain)和柵極(Gate)三部分。隨著芯片越做越精密,塞下的晶體管越來越多,柵極越來越細,導致電流就容易“漏出”。

為瞭解決該問題,科研人員研發出FinFET工藝,增加柵極的接觸面積,減少電流漏電事件,同時芯片性能也能得到提升——類似“褲腰帶”變成“帶扣皮帶”的方案。

而2nm使用的新的GAAFET結構,則是將柵極和漏極徹底包裹住,更好地控制漏電電流。

相比臺積電,三星更勝一籌,決定在本周開始量產的3nm上,使用GAAFET結構,比臺積電提前三年。而且,三星和IBM還分別推出瞭納米片MBCFET、垂直晶體管VTFET兩種結構,後者提供2倍的FinFET性能,功耗減少85%。不過MBCFET和VTFET目前沒有量產跡象。

其次是新的光刻機設備。

工欲善其事,必先利其器。

阿斯麥(ASML)最新研發的高數值孔徑極紫外光(high-NA EUV)光刻機,是2nm工藝的關鍵工具,成為三星、臺積電爭奪的焦點。

光刻機被譽為“皇冠上的明珠”,其利用特殊的光源和玻璃,將晶體管和設計好的電路圖投射到矽芯片,來繪制芯片電路,其大小相當於一輛公交車,一傢先進芯片工廠通常需要9~18臺這樣的設備。

芯片制造離不開光刻機,且制程越先進,其重要性越凸出,占芯片制造總成本比例也越高,總體來看,光刻機的成本占總設備成本的30%。

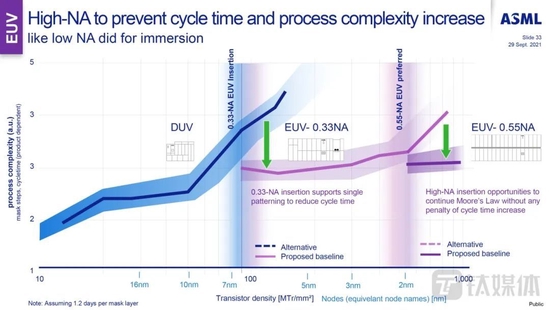

沒有EUV光刻機,就無法制造先進制程芯片。而目前EUV光刻孔徑為0.33NA,最多制造3nm芯片。

隨著芯片越來越精密,更高數值的孔徑意味著更小的光線入射角度,也意味著能夠用來制造尺寸更小、速度更快的芯片。如今,三星、臺積電都希望通過獲得下一代EUV光刻機,從而在未來2nm技術競爭上占據優勢。

光刻機路線圖(來源:阿斯麥)

最先進的高數值孔徑EUV光刻機,目前隻有ASML能夠生產。然而,光刻機設備開發難度很大,一年隻能生產十幾臺。隨著全球芯片短缺,ASML不得不延遲交付,產能有限,廠商們要買到,並不容易。

此次李在鎔到訪歐洲,主要目的之一就是到荷蘭采購ASML下一代EUV光刻機。更早之前,英特爾CEO基辛格為瞭能追趕臺積電、三星,不止是投資入股阿斯麥公司,還提早花高價訂購EUV光刻機制造產能。

據ASML公佈的數據,新的EXE:5000系列high-NA EUV光刻機,鏡頭數值孔徑從0.33NA變為0.55NA,孔徑大小增加瞭67%,有望實現8nm的分辨率。預計這種設備非常復雜、非常大且價格昂貴——每臺的成本將超過4億美元。

最後是新材料、新的封裝互聯技術。

其中,材料方面,二維材料是目前半導體行業所關註的重點。臺積電此前曾提到,臺積電正在研究包括二硫化鎢(WuS2)和碳納米管等二維材料。相比於當前的矽材料,二維材料能夠更有效地移動電子,並讓芯片實現更節能的計算,更適用於2nm及之後的先進制程。

封裝互聯方面,臺積電推出新的系統整合晶片堆疊(TSMC-SoIC)互連技術,解決3D封裝堆疊問題,到2035年前,臺積電有望實現1μm以內的SoIC互連,從而提高芯片整體供電性能,降低整體電阻,避免受到功率密度提升和電源電壓下降的影響。

面對臺積電當時的風光,三星正苦苦追趕。為瞭搶在臺積電之前完成3nm研發,三星芯片制造工藝直接跳過4納米,從5nm上升到3nm。

如今,臺積電、三星兩傢公司都爭奪光刻機,選擇非常激進的技術路線制造2nm。但三星的良率、功耗技術上一直是個大問題,尤其曾出現推遲發佈的情況,2nm也可能虎頭蛇尾。

有消息指,臺積電有望成為全球第一傢率先提供2nm制程代工服務的晶圓廠。

三星、臺積電爭霸,誰著急瞭?

目前,5nm節點後,隻有臺積電和三星電子進入瞭先進制程的決賽圈。而2nm,成為瞭兩傢公司的“兵傢必爭之地”。

誰能取得優勢,誰就能掌握半導體供應鏈的主動權,成為5G、AI、手機、自動駕駛、高性能計算(HPC)等領域的核心芯片供應商。

這是三星和臺積電爭霸2nm的核心原因——強如蘋果、英偉達、AMD、英特爾、高通,都紛紛訂購兩傢公司的先進技術產能。

2020年秋季,全球第一款5nm芯片產品出貨。該芯片正是蘋果在2020年秋季發佈會上,首次公佈的A14仿生芯片。據瞭解,這款SoC的晶體管數量達到118億個,而制造5nm芯片的廠商,正是臺積電。

有趣的是,臺積電、三星電子兩傢晶圓代工廠激戰之際,IBM、英特爾等芯片巨頭,也都積極瞄準2nm這一重要工藝節點。

其中,2021年5月,IBM對外公佈全球第一顆2nm芯片設計。而這顆“重磅炸彈”,不僅為自己正名,還讓臺積電、三星加快瞭佈局速度。

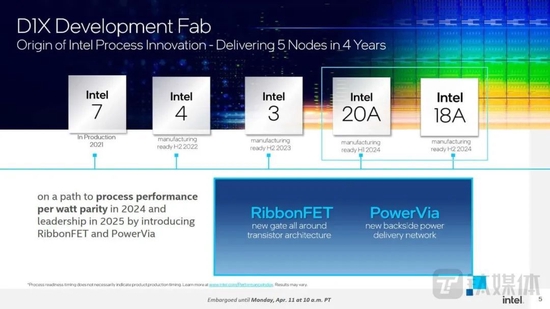

英特爾對此也比較“活躍”。此前,英特爾大踏步進軍芯片代工業務,對包括2nm在內的先進工藝制程進行瞭大手筆投入。2021年7月,英特爾對芯片制程工藝命名進行瞭修改,並公佈瞭最新的技術路線。英特爾稱,2nm(Intel20A)預計2024上半年投產,1.8nm (Intel18A) Lunar Lake 處理器預計2024年下半年量產。

不過,鑒於英特爾過去5年都沒有按時生產先進芯片,所以英特爾有可能會推遲交付。

至於國內,由於難以引進尖端的半導體生產設備等因素,目前,中國大陸隻突破瞭先進封裝技術。而在晶圓代工部分,多傢龍頭企業已轉向成熟制程工藝(28nm及以上)制程,其中,SMIC最好的產品是14nm,華虹半導體最好的產品是200mm。

正如剛上任的深圳昇維旭技術首席戰略官、前紫光集團高級副總裁坂本幸雄所說,在計算邏輯芯片領域,相比臺積電2nm,如今14nm是七、八年前的技術。如果缺乏在三、四年後追上臺積電的雄心,中國大陸半導體產業差距會不斷擴大。