三星半導體這幾年,小日子過的有些不順。別的不說,差友摸摸自己的手機,看看三星晶圓廠代工的888、8gen1,簡直可以說是冬天的暖手寶,夏日的燙手山芋。好不容易代工出來的產品成瞭人人喊打的“過街老鼠”,而且芯片生產的良品率也不行。甚至就連三星自己都心頭納悶啊,事後會過味來,你說為啥我自個的芯片工藝,良品率會這麼差呢?

這不,上上上上個月展開瞭調查,結果到現在也還沒個說法。

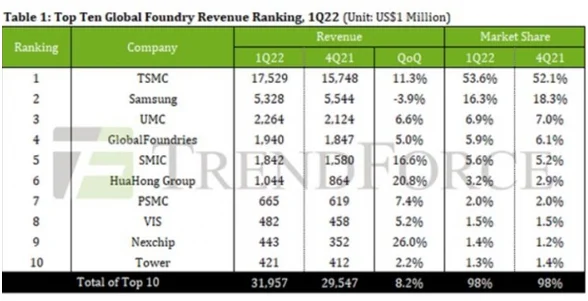

而且作為全球十大半導體公司,在大傢都在喊著缺芯缺芯的時候,三星反而成瞭 唯一一個第一季度收入下降的公司……

看著上頭的臺積電,羨慕的臉都要綠瞭。

所以說,當年這能造相機,能造手機,能做系統,也能做芯片的三星,這幾年到底遭瞭什麼降頭?

手機行業吃瞭鱉,面板行業被國內廠商逐漸挑戰,放棄瞭自傢的芯片架構, 就連世界上唯二能量產 5nm 以下工藝的芯片代工行業,都被大傢嫌棄的如此之慘?

作為一傢傳承多年的公司,三星這幾年拉跨的表現可以說和 內鬥脫不瞭關系。

這幾年下來,我們也能刷到不少這類三星新聞,包括什麼良品率不足欺上瞞下啊,什麼論資排輩,部門之間還互相嫌棄…… 咱能想到的想不到的內鬥方式,三星可能都已經嘗試過瞭。

這把三星太子急的, 2021 年 8 月李在鎔 “ 為國 ” 出獄後,還沒三個月,公司內部就來瞭一波不小的人事調整。

三星移動部門,三星消費電子和設備解決方案部門的三位 CEO 都被撤下,還將前兩個部門合並成為瞭新部門 SET 。

又過瞭一段時間,李在鎔還把之前閃存開發部門的領導宋在赫調到瞭 半導體研發部門擔任最新的負責人,派半導體設備解決方案部門的全球制造與基礎設施副總裁南錫宇,來出任 晶圓代工制造技術中心負責人。

把過去這兩位在 內存領域搏殺的大將給派到晶圓代工領域,三星這圖謀半導體之心,可以說是非常明顯瞭。

畢竟,如果再和過去一樣內鬥會是什麼結果,已經很明顯瞭。

比良品率下降更恐怖的,就是讓 先進制程的買傢失去信心。

高通和英偉達,在這裡扮演的就是三星的大買傢角色。

然而如今這倆一個已經跟臺積電合作,緊急推出瞭 8+Gen1 來應對今年聯發科的崛起,一個宣佈下一代 40 系列遊戲顯卡也會基於臺積電的 N4 工藝開發。

圖源:wccftech▼

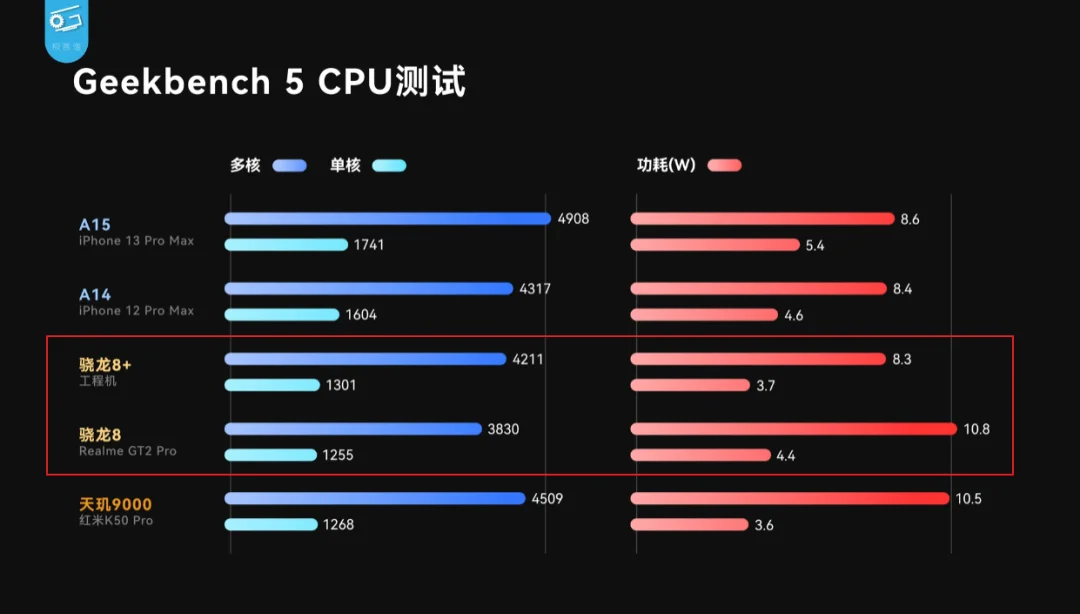

不久之前也有媒體拿到瞭 8+Gen1 的工程機測瞭一下,和之前三星代工的 8Gen1 相比呢……也就性能高瞭一點,功耗更低瞭一些……

這屬實是撞車不可怕,誰差誰尷尬瞭。

圖源極客灣▼

差評君還聽到一個芯片行業地獄笑話:

過去大傢做芯片呢,是一手交錢,一手按消耗的晶圓數量來給你生產,各傢有各傢的良品率,能做出多少芯片全憑良品率來摸獎,大傢相安無事好多年。

而到瞭三星這邊,因為良品率實在不好恭維。所以它們變成瞭按照最後實際能生產出多少芯片來計算……

一手交錢,一手交芯片。

……的確是讓三星自個兒都納悶為啥這麼差的良品率瞭。

當然,芯片工藝, 敗也技術,成也技術。

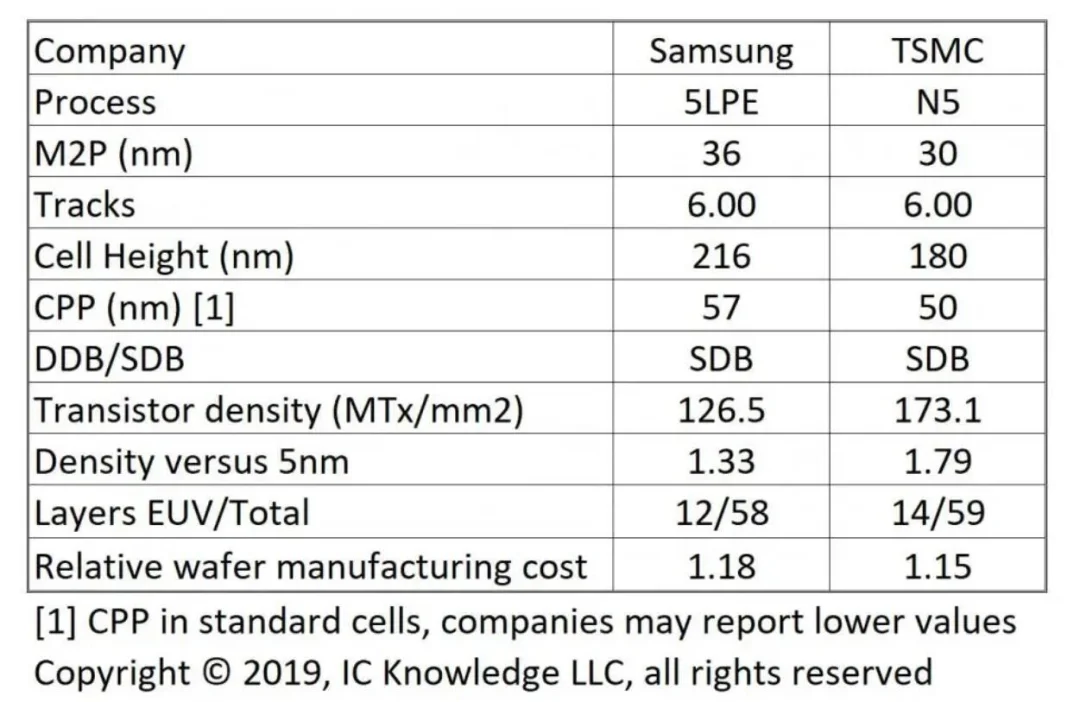

畢竟現在 5nm , 4nm 的名稱,更多還是廠商用來宣傳自己的工藝節點的一種叫法,而並沒有絕對的物理意義指代。

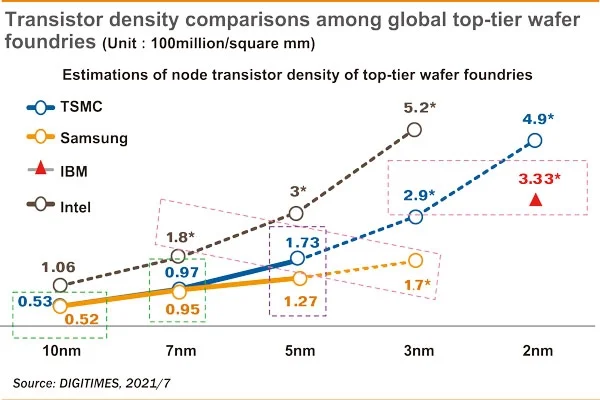

為啥三星現在這麼尷尬,很大程度上就是因為最新的芯片造的不如隔壁臺積電好, 良品率,功耗,晶體管密度都幹不過別人。

各傢工藝密度圖,來源:Digtimes▼

所以,如果下回三星造的芯片 良品率更好, 功耗更低, 晶體管密度更優秀,那這些煩人的問題不就都解決瞭嗎。

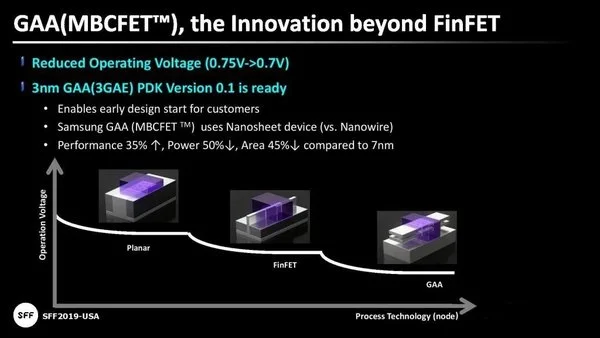

巧瞭,三星也是這麼想的,而它們壓註的未來,就是 3nm 技術。

三星,將是世界上第一個邁入 GAA 結構的晶圓廠。

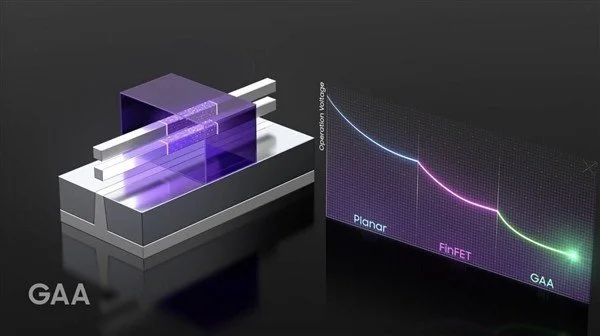

GAA 是啥?簡單來講,它很可能是我們手機 SoC 上會采用的下一代晶體管技術。

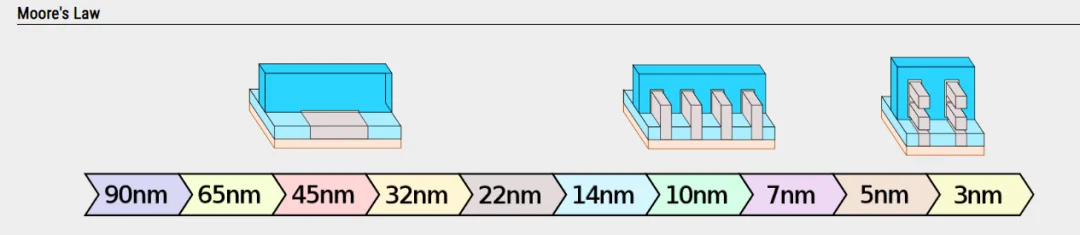

這幾年, 隨著摩爾定律的演變,芯片越做越小瞭,晶體管的功耗也越來越低,但是隨著晶體管越來越小吧,新的問題——漏電也如期而至。

隨著芯片設計進入納米領域之後, 靜態功耗的漏電問題就開始翻車。

打個比方,如果把晶體管看作一個 “ 開關 ” ,那漏電問題就像是這個 開關沒接通, 但是還會存在漏電流。

這就是 “ 短溝道效應 ” ,想要減少它帶來的漏電功耗,就需要找到新的結構或者新的材料。

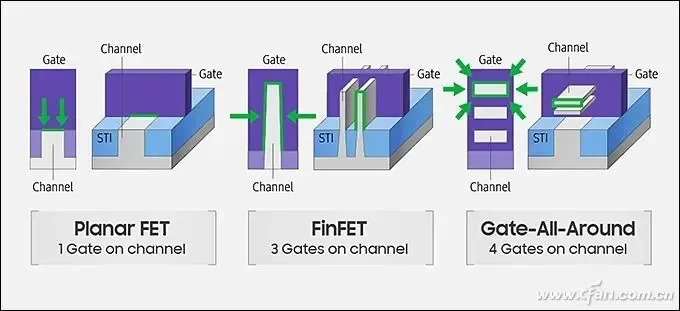

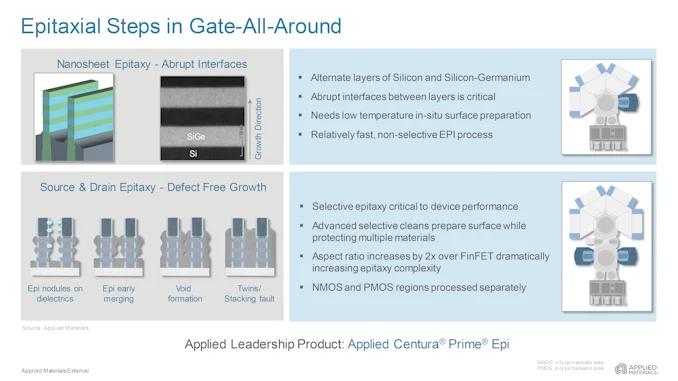

在把芯片做到 22nm 之後,大傢采用的技術叫做 FinFET ( 鰭式場效應晶體管 )。

通過 “ 嵌入 ” 的方式 增大接觸面積,來獲得更好的漏電控制性能,有點像把之前一維的晶體管做成二維。

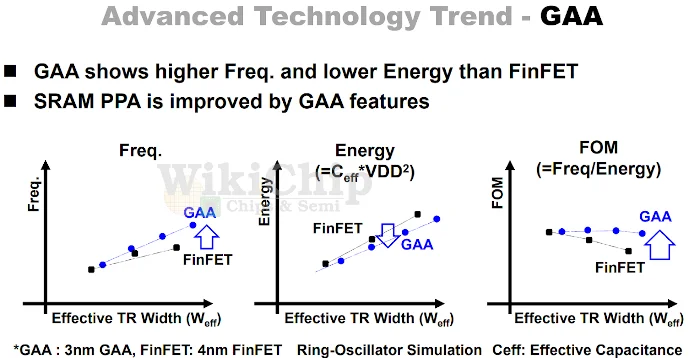

而如今芯片越來越小,做到 3nm 的門檻上, FinFET 也不太夠用瞭。

而這回,大傢夥倒騰出來解決問題的未來新工藝,叫做 GAA ( 全環柵晶體管 )。

這個就有點像二維變成瞭三維, FinFET 時的三面環繞變成瞭四面環繞,這樣才能對蠢蠢欲動的電子一網打盡。

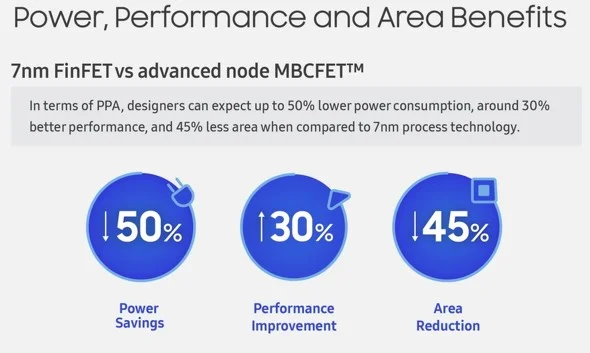

根據三星的報道,和自傢的 7nm 工藝相比,自傢 GAA 的初始版本 3GAE ( 3nm Gate-All _ Around Early )可以減少 35% 的芯片面積,提高 30% 的性能,降低 50% 的功耗。

這餅看著挺香啊……提升 30% 的性能,降低 50% 的功耗……有這提升,啥火龍不得乖乖躺下,給咱們變成冰龍。

欸不是,等等等等,你咋是和 2017 年量產的 7nm 工藝來比 3nm 的,為啥不用明顯更接近的 4nm ?

好吧,其實是三星也給瞭 3nm 和 4nm 工藝的技術對比, 但是——沒有完全給。

對比圖的的確確是給瞭一張,但是吧……也隻有這一張,這橫縱坐標的標尺呢?比較的起始單位又是多少?

你倒是告訴我強瞭多少啊?

作為在 GAA 領域 “ 第一個吃螃蟹的人 ” 咱能理解三星會面臨不少的技術挑戰。

但是你看看三星計劃要量產 3nm 的時間哈, 2022 年第二季度。

本來自傢的 5nm 和 4nm 相比臺積電就有些註水,在晶體管密度上就有些落後。

不知道三星這算不算 “ 趕鴨子上架 ” 整出來的初代的 GAA 能否和臺積電的高密度成熟 finFET 來競爭,可能還得打個問號。

在過去, 新工藝迭代節點的第一批產品,也出現過實際體驗的性能反而比不過 上一代工藝增強節點產品的情況。( 比如英特爾 10nm 和 14++ )

除開兩傢公司技術路線的不同,三星想要在 3nm ,或者 2nm 階段實現對臺積電的反擊,還得過光刻機這一關。

在這方面。

臺積電和A SML 可以說是有深厚的革命戰友友誼。

20 年前的 ASML 在光刻領域還是名不見經傳,靠的就是和臺積電的深度合作,在對的時間遇到瞭對的人。

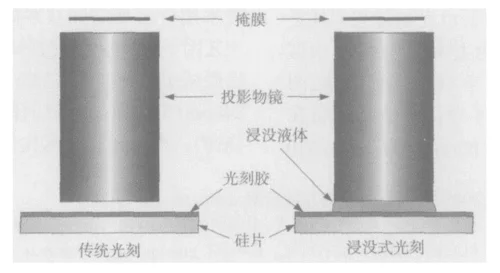

兩傢公司一起攜手發展 193nm 浸潤式光刻技術。把曾經的光刻機巨頭尼康給趕瞭出去。

從 20 年前的 45nm 到前些年的 7nm 工藝,靠的都是浸潤式光刻技術。

三星可不像臺積電有這層關系,隻得看著光刻機眼紅,另尋它法。

你看出獄沒多久,剛整治完內部的李在鎔,上周前往歐洲諸國,別的地方沒多停留,直接就跑到荷蘭去,跟 ASML 的高層與荷蘭的總理談笑風生。

這一切的目的,都是為瞭最新的 EUV ( 極紫外光 )光刻機。

總的來說,三星雖然如今在 5nm , 4nm 的市場失去瞭先機,但也不代表著它完全失去瞭反擊的機會。

畢竟,芯片行業是個競爭異常緊湊的市場,曾經的頭牌如果走錯一步,可能就會在下一代工藝裡失去領先的優勢。

萬一臺積電的 3nm FinFET 如果真的因為控制不住功耗翻車瞭呢?

“ 王權沒有永恒 ” ,在這個行業裡,領頭羊走岔路可謂是傢常便飯。

在過去, 14nm 工藝門後的英特爾是如此,在現在, 7nm 門前的三星也是如此,在未來,在 3nm 門檻上依舊堅持選擇用 FinFET 的臺積電可能也如此。

但不論如何,把翻身的機會寄希望於別人翻車是不靠譜的。

2022 年的 Q2 季度已經過瞭一半多,現在留給三星的時間已經不多瞭。