昨天,世界著名的半導體巨頭三星,宣佈瞭一條大新聞。基於3納米(nm)制程的芯片,正式量產瞭!在紙面參數上,可謂是實現瞭質的飛躍——性能猛提30%,功耗猛降50%,面積也減少瞭35%。

來源:新智元

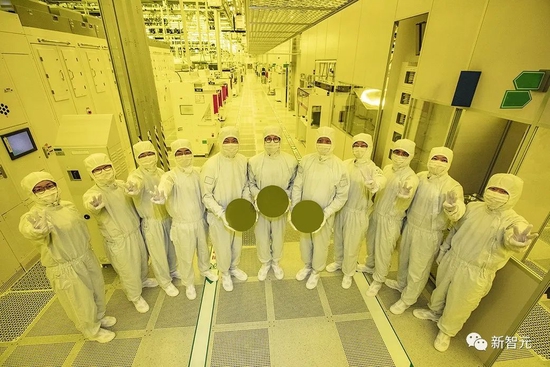

中間三位大咖抱的可不是普通的“盤子”,而是剛從三星華城電子園區生產線上拿下來的3納米晶圓。

再看看周圍的其他團隊成員,笑得也相當開心。而且他們比的不是剪刀手,而是代表著3納米的“3”。

性能拉滿,能耗暴降

說起這個首次實現量產的3納米芯片,就不得不提到它背後的MBCFET技術。

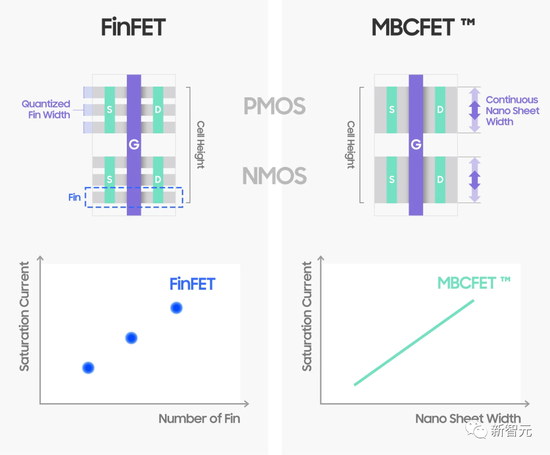

MBCFE突破瞭此前FinFET的性能限制,通過降低電源電壓水平來提高功率效率,同時還通過增加驅動電流能力提高瞭性能。

說起納米片晶體管和半導體芯片的應用,三星這還是第一次。目的是為瞭實現高性能、低功耗的計算服務。最終能在移動處理器上也得以應用。

三星的總裁,兼代工業務負責人Siyoung Choi博士表示,“我們一直都發展得很快。三星一直緊跟前沿的技術,然後想辦法把它們投入生產應用。比如說之前的首個High-K金屬柵極、FinFET,還有EUV等等。”

“現在,我們又是第一個研究MBCFET的。”

三星的獨傢技術應用瞭有更寬的通道的納米片,和用通道窄一點的納米線的傳統GAA技術相比,不光提升瞭性能,還提高瞭能源利用率。

不僅如此,應用瞭3納米GAA技術,三星還能通過調整納米片的通道寬度,優化功耗和性能,來滿足各類客戶的不同需求。

此外,3納米GAA的設計非常靈活,簡直就是為設計技術協同優化(DTCO)量身打造的。我們主要看新技術應用以後,芯片的功耗、性能和面積大小(PPA,Power、Performance、Area)三個維度來量化。

和5納米的工藝相比,第一代3納米工藝相比5納米降低瞭高達45%的能耗,提升瞭23%的性能,減少瞭16%的面積。

光是一代的提升就已經肉眼可見瞭。

更不用說二代的PPA——功耗降低50%、性能提高30%、面積減少35%,比一代又優秀瞭不知多少。

良品率行不行?量產靠譜嗎?

在外行眼裡,能量產3納米的工藝可能已經不敢想象瞭,但是也有分析師表達瞭其它的一些看法。

來自大和資本市場的SK Kim表示,“三星能幹成這件事,確實有意義。但還遠遠不夠。量產隻是第一步,你在能用它來生產主流芯片之前,比如手機CPU這種,不見得能多掙多少錢。”

這其實是有根據的。

4月份就有消息傳出來,說三星基於GAA的3納米工藝良率才在10%~20%之間,比預期低得多。

三星需要付出更多的精力和成本來解決這個問題。

5月份就再次傳出瞭3納米良率問題已得到解決的消息,6月初才又傳出來進入試驗性量產的說法。

不過,有瞭4月的前車之鑒,業界很多專傢都對三星3納米的真實情況打瞭個小小的問號。

據報道,6月22日,市場再次傳出瞭三星3納米芯片量產再一次推遲的消息,還是因為良率問題。

而且,三星之前給別的大廠代工芯片還鬧出過不少笑話。

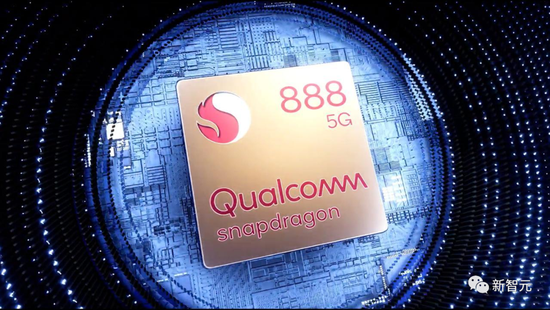

最逗的可能就是當時超級出圈的驍龍888,人送外號“大火龍”。

(圖:大火龍真身)

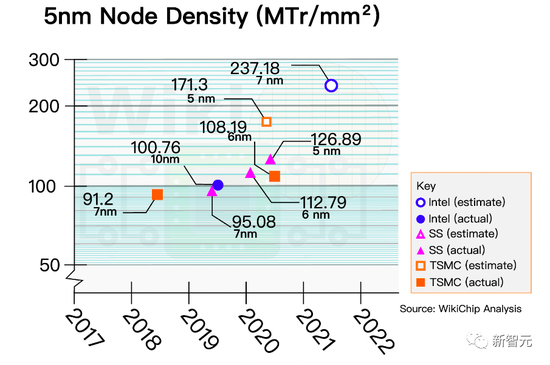

當時高通找到三星來代工生產這款芯片的時候,沒想到三星這麼能搞。雖然當時都是5納米工藝,但是三星和臺積電的5納米可差得太多瞭。

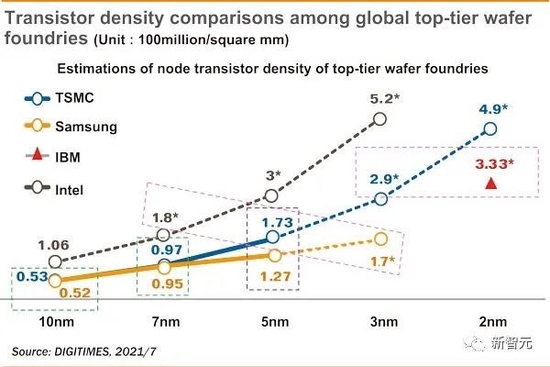

數據顯示,三星5納米的晶體管密度每平方毫米隻有127萬個晶體管,而臺積電達到瞭173萬個。差瞭46%。

說來好笑,“大火龍”用起來熱的把CPU都燒的虛焊瞭。

可見,拋開別的不談,三星在芯片制作這方面,總感覺差點意思。

但不管怎麼說,就3納米工藝而言,技術歸技術,該先進還是先進。

拋棄FinFET,首次采用GAA技術

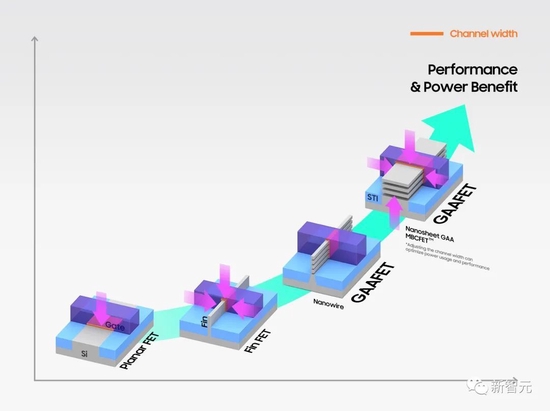

相比於傳統芯片采用的“FinFET”技術而言,三星采用的“GAAFET”技術明顯占據優勢。

“FinFET”技術已經在芯片上使用瞭將近10年時間,它幫助芯片完成瞭從28納米工藝到5納米工藝的跨越。

相比之下,“GAAFET”的溝道被柵極四面包圍,溝道電流比三面包裹的“FinFET”更加順暢,這樣的設計進一步改善瞭對電流的控制,從而優化柵極長度的微縮。不僅消耗功率低,耗電量低,速度也更快瞭。

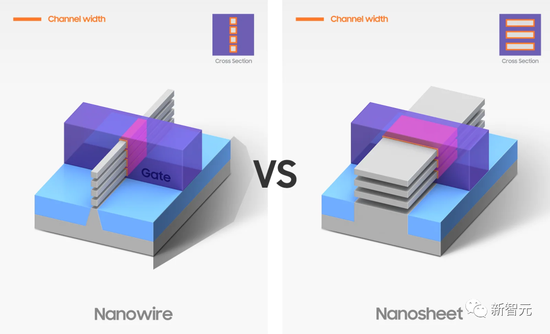

三星認為采用納米線溝道設計必須堆疊更多的線層以增加總溝道寬度,這樣的工藝不僅復雜,且付出的成本可能也大於收益。

因此,三星設計瞭一種全新的GAA形式——MBCFET(Multi-Bridge-Channel FET,多橋-通道場效應管),采用多層堆疊的納米片(Nanosheet)來替代“GAAFET”中的納米線(Nanowire)。

“MBCFET”采用瞭具有更大寬度的片狀結構,同時保留瞭所有“GAAFET”優點,實現瞭最小化復雜度。

基於納米片的“MBCFET”具有極高的可定制性,納米片的寬度是定義功率和性能特性的關鍵指標,即納米片的寬度越大,它的性能就越高。

因此,專註於低功耗的晶體管設計可以使用更小的納米片,而需要更高性能則可以使用更寬的納米片。

現在我們再來看一下此時的臺積電老大哥有什麼進展。

臺積電在3納米制程工藝上並沒有選擇GAA架構的晶體管,而是依然采用“FinFET”,通過復用之前成熟穩定的技術,這會為臺積電的產品帶來更好的穩定性,同時也能更好的控制成本,使利益最大化。

最關鍵的是,這樣的操作可以給臺積電爭取更多時間實現對GAA晶體管架構的優化。

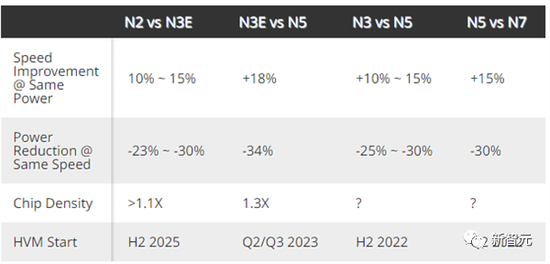

根據臺積電此前“2022年臺積電技術論壇”上公佈的數據顯示,其依然采用FinFET晶體管架構的3納米的制程工藝,相比前代的5納米制程工藝,性能將提升18%,功耗可降低34%,晶體管密度可提升30%。

從表中也可以看出,臺積電的2納米制程的部分技術指標:相較於3納米的低成本版工藝,在相同功耗下,臺積電2納米工藝的性能將提升10~15%;而在相同性能下,臺積電2納米工藝的功耗將降低23~30%;晶體管密度僅提升瞭10%。

得此提升的原因主要是,在晶體管架構方面,臺積電N2拋棄瞭“FinFET”,采用瞭全新的納米片晶體管架構,即臺積電版的“GAAFET”。

去年,Digitimes表明,三星3nm工藝可達成的晶體管密度大約為170 MTr/mm²(百萬晶體管每平方毫米);而臺積電早在5nm時代就已經將晶體管密度推進到瞭173 MTr/mm²。

另外Wikichip去年年中預測:臺積電3nm工藝的晶體管密度可以達到291.21 MTr/mm²,在Digitimes的這張表裡看起來也差不多。

如果三星3nm工藝真的隻有表中170 MTr/mm²的程度,那麼這和臺積電的差距,就一目瞭然瞭!

最終,臺積電的3納米到底會帶來多強烈的“震撼”,我們拭目以待!