據臺媒經濟日報報道,臺積電致股東營業報告書今(5)日上傳,報告提及臺積電技術發展,正為預計於2025年開始量產的2nm技術(N2)做準備,該制程技術將座落於新竹和臺中科學園區。

技術發展方面,臺積電致股東營業報告書說,公司的N2技術提供全制程效能和功耗效率的效益;相較於N3E,N2在相同功耗下速度增快10%-15%,或在相同速度下功耗降低25%-30%,臺積電期盼以此進一步擴展公司未來的技術領先地位。報告提到,N2技術的研發依計劃進行中,預計於2024試產,並於2025年量產。

臺積電致股東營業報告書提到, N5傢族技術已邁入量產的第三年,為臺積電營收貢獻26%,公司持續強化N5傢族的效能、功耗和密度;N4已於2022年開始量產,且公司也為支持下一波的N5產品,推出N4P和N4X制程技術。N4P制程技術研發進展順利,預計於2024量產。

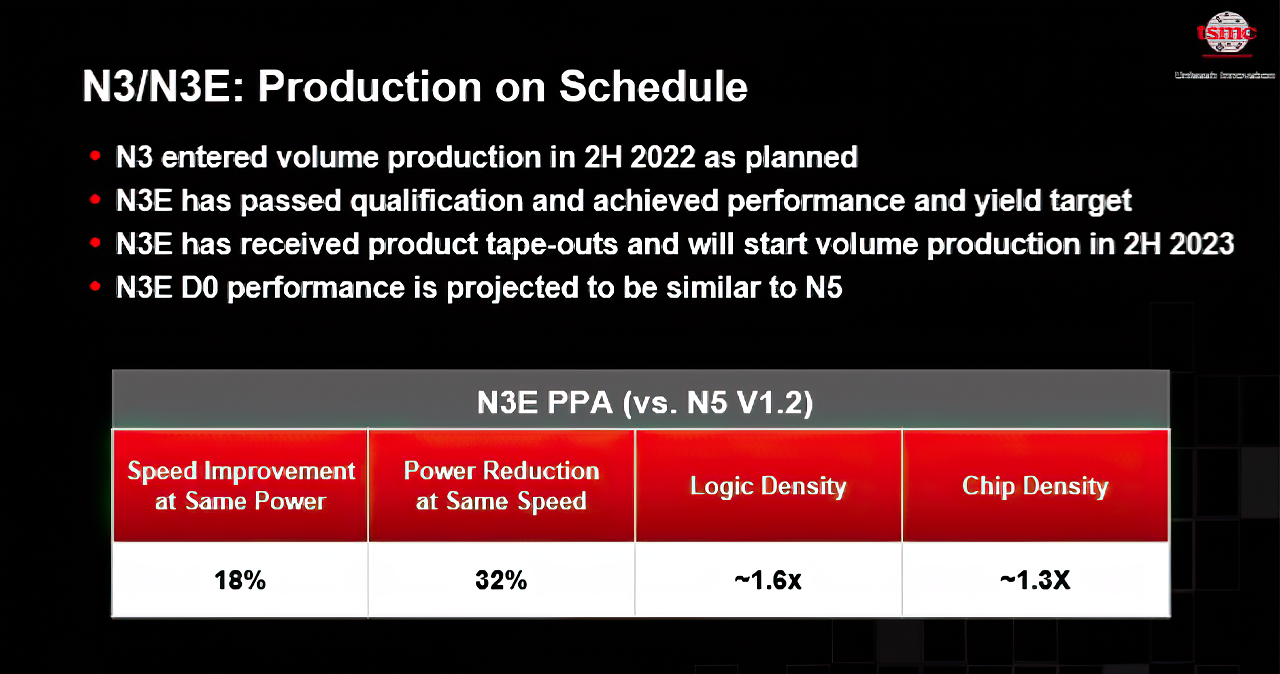

繼N3技術於2022年進入量產,N3E預計於2024下半年量產。臺積電特別提到,N3和N3E客戶參與度非常高,量產第一年和第二年的產品設計定案數量將是N5的兩倍以上。公司預期N3傢族將成為臺積電另一個大規模且有長期需求的制程技術。

據臺媒中央社此前報道,臺積電於美國時間26日舉辦北美技術論壇。臺積電總裁魏哲傢在會上表示,N3E、N3AE制程預計於今年量產;強化版N3P制程預計2024年下半年量產;N2制程在良率和元件性能進展良好,將如期於2025年量產;N3X制程預計於2025年進入量產。

此外,先進封裝方面,臺積電正在開發具有高達6個光罩尺寸(約5000平方毫米)重佈線層(RDL)中介層的CoWoS解決方案,能夠容納12個高頻寬存儲堆疊。三維芯片堆疊部分,臺積電推出SoIC-P,作為系統整合芯片(SoIC)解決方案的微凸塊版本,提供具有成本效益的方式來進行3D芯片堆疊。