美國當地時間4月24日,臺積電在美國舉辦“2024年臺積電北美技術論壇”,披露其最新的制程技術、先進封裝技術、以及三維集成電路(3DIC)技術,憑借此領先的半導體技術來驅動下一代人工智能(AI)的創新。

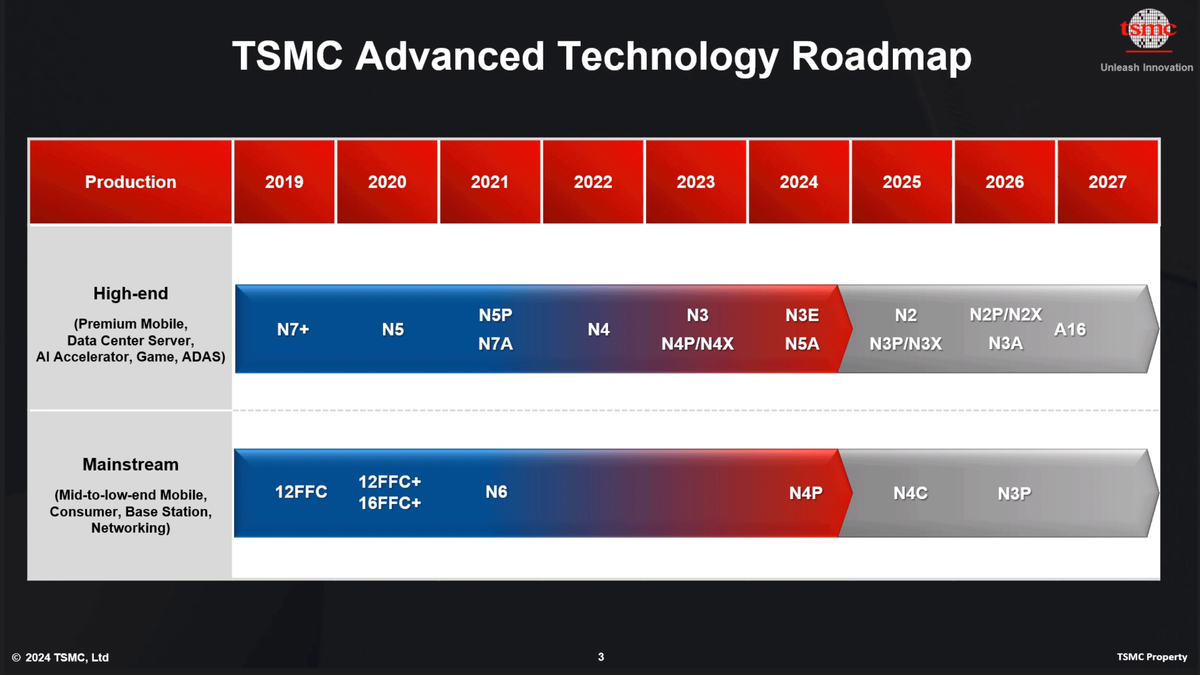

據解,臺積電在此次的北美技術論壇中,首度公開臺積電A16(1.6nm)技術,結合領先的納米片晶體管及創新的背面供電(backside power rail)解決方案以大幅提升邏輯密度及性能,預計於2026年量產。

臺積電還推出系統級晶圓(TSMC-SoWTM)技術,此創新解決方案帶來革命性的晶圓級性能優勢,滿足超大規模數據中心未來對AI的要求。

臺積電指出,適逢臺積電北美技術論壇舉辦30周年,出席貴賓人數從30年前不到100位,增加到今年已超過2,000位。

北美技術論壇於美國加州聖塔克拉拉市舉行,為接下來幾個月陸續登場的全球技術論壇揭開序幕,本技術論壇亦設置創新專區,展示新興客戶的技術成果。

臺積電總裁魏哲傢博士指出,我們身處AI賦能的世界,人工智慧功能不僅建置於數據中心,而且也內置於個人電腦、移動設備、汽車、甚至物聯網之中。

臺積電為客戶提供最完備的技術,從全世界最先進的矽芯片,到最廣泛的先進封裝組合與3D IC平臺,再到串連數位世界與現實世界的特殊制程技術,以實現他們對AI的願景。

此次論壇公佈新技術包括:

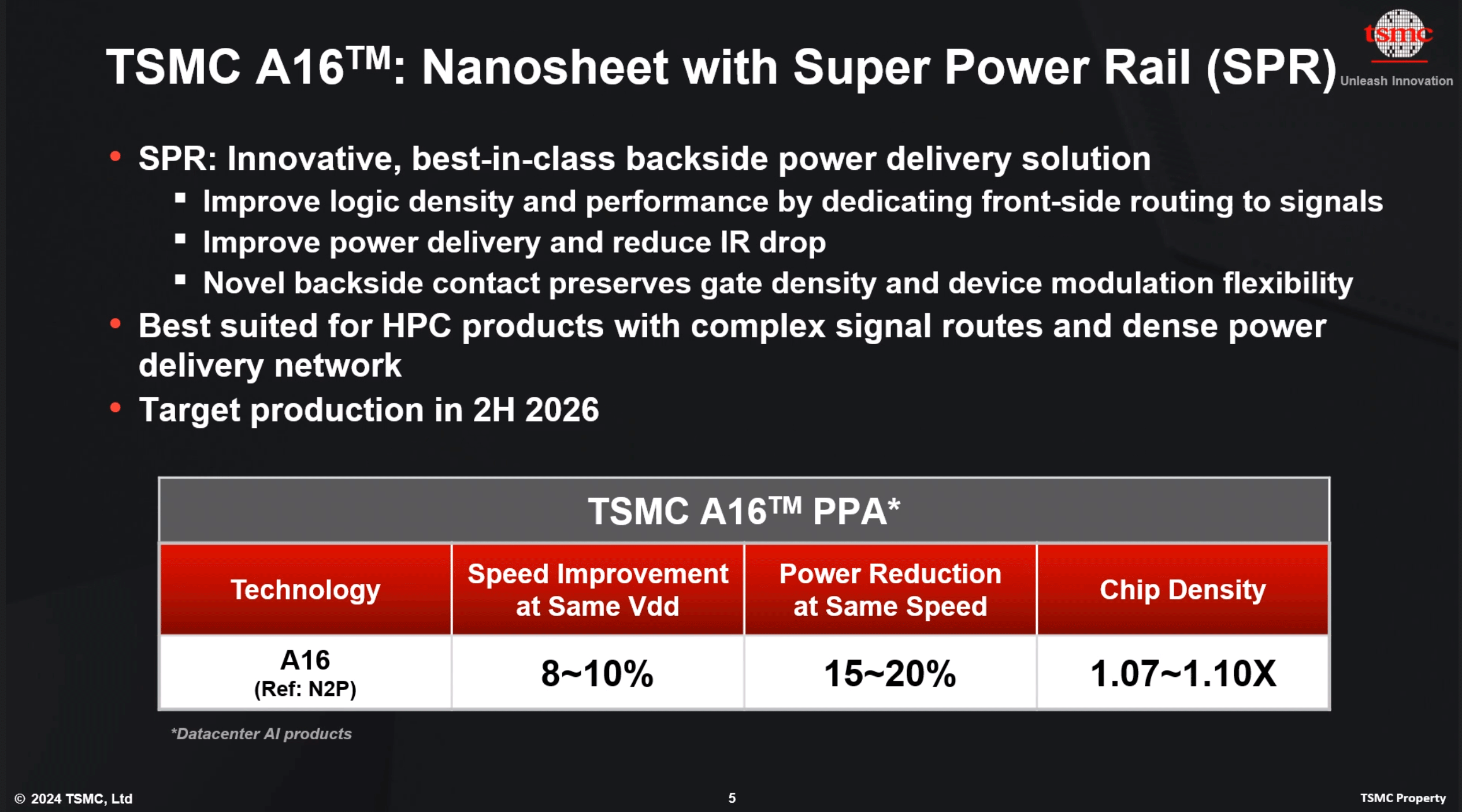

臺積電A16技術

隨著臺積電領先業界的N3E技術進入量產,接下來的N2技術預計於2025年下半年量產,臺積電在其技術藍圖上推出新技術A16。

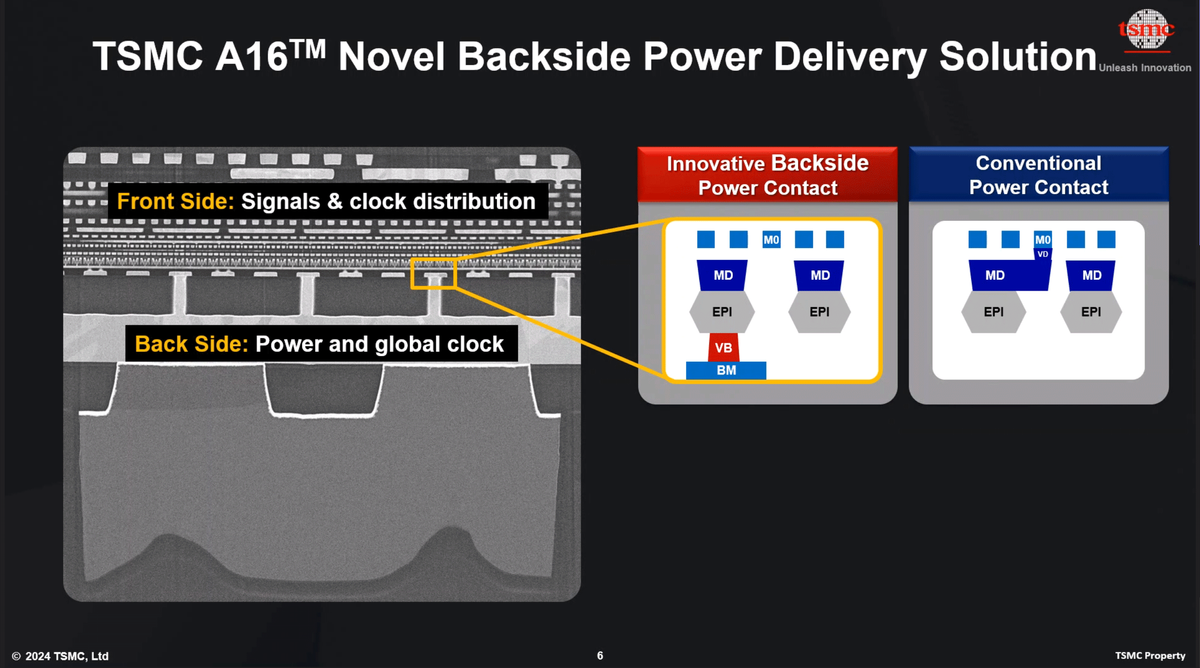

據介紹,A16將結合臺積電的超級電軌(Super PowerRail)構架與納米片晶體管,預計於2026年量產。

該超級電軌技術將供電網絡移到晶圓背面,為晶圓正面釋放出更多信號網絡的佈局空間,借以提升邏輯密度和性能,讓A16適用於具有復雜信號佈線及密集供電網絡的高效能運算(HPC)產品。

臺積電表示,相較於N2P制程,A16在相同Vdd(工作電壓)下,速度增快8-10%,在相同速度下,功耗降低15-20%,芯片密度提升高達1.10倍,以支持數據中心產品。

臺積電創新的NanoFlex技術支持納米片晶體管

臺積電即將推出的N2技術將搭配TSMC NanoFlex技術,展現臺積電在設計技術協同優化的嶄新突破。

TSMC NanoFlex為芯片設計人員提供靈活的N2標準元件,這是芯片設計的基本構建模塊,高度較低的元件能夠節省面積並擁有更高的功耗效率,而高度較高的元件則將性能最大化。

客戶能夠在相同的設計內存塊中優化高低元件組合,調整設計進而在應用的功耗、性能及面積之間取得最佳平衡。

N4C技術

臺積電還宣佈將推出先進的N4C技術以因應更廣泛的應用。

N4C延續N4P技術,晶粒成本降低高達8.5%且采用門檻低,預計於2025年量產。

據介紹,N4C提供具有面積效益的基礎矽智財及設計法則,皆與廣被采用的N4P完全兼容,因此客戶可以輕松移轉到N4C,晶粒尺寸縮小亦提高良率,為強調價值為主的產品提供具有成本效益的選擇,以升級到臺積電下一個先進技術。

CoWoS、系統整合芯片、以及系統級晶圓(TSMC-SoW)

臺積電的CoWoS是AI革命的關鍵推動技術,讓客戶能夠在單一中介層上並排放置更多的處理器核心及高帶寬內存(HBM)。

同時,臺積電的系統整合芯片(SoIC)已成為3D芯片堆疊的領先解決方案,客戶越來越趨向采用CoWoS搭配SoIC及其他元件的做法,以實現最終的系統級封裝(System in Package,SiP)整合。

臺積電系統級晶圓技術提供一個革新的選項,讓12英寸晶圓能夠容納大量的晶粒,提供更多的運算能力,大幅減少數據中心的使用空間,並將每瓦性能提升好幾個數量級。

臺積電已經量產的首款SoW產品采用以邏輯芯片為主的整合型扇出(InFO)技術,而采用CoWoS技術的芯片堆疊版本預計於2027年準備就緒,能夠整合SoIC、HBM及其他元件,打造一個強大且運算能力媲美數據中心服務器機架或甚至整臺服務器的晶圓級系統。

矽光子整合

臺積電正在研發緊湊型通用光子引擎(COUPE)技術,以支持AI熱潮帶來的數據傳輸爆炸性成長。

COUPE使用SoIC-X芯片堆疊技術將電子裸晶堆疊在光子裸晶之上,相較於傳統的堆疊方式,能夠為裸晶對裸晶界面提供最低的電阻及更高的能源效率。

臺積電計於2025年完成支持小型插拔式連接器的COUPE驗證,接著於2026年整合CoWoS封裝成為共同封裝光學元件(Co-Packaged Optics,CPO),將光連接直接導入封裝中。

車用先進封裝

繼2023年推出支持車用客戶及早采用的N3AE制程之後,臺積電藉由整合先進芯片與封裝來持續滿足車用客戶對更高運算能力的需求,以符合行車的安全與質量要求。

臺積電正在研發InFO-oS及CoWoS-R解決方案,支持先進駕駛輔助系統(ADAS)、車輛控制及中控電腦等應用,預計於2025年第四季完成AEC-Q100第二級驗證。