三星半導體業務高管前幾天表態要用5年時間趕超臺積電,實現這個目標就離不開先進工藝,去年6月份三星就宣佈全球首發3nmGAA工藝,日前該公司又推出第二代3nm工藝,預計在2024年量產。

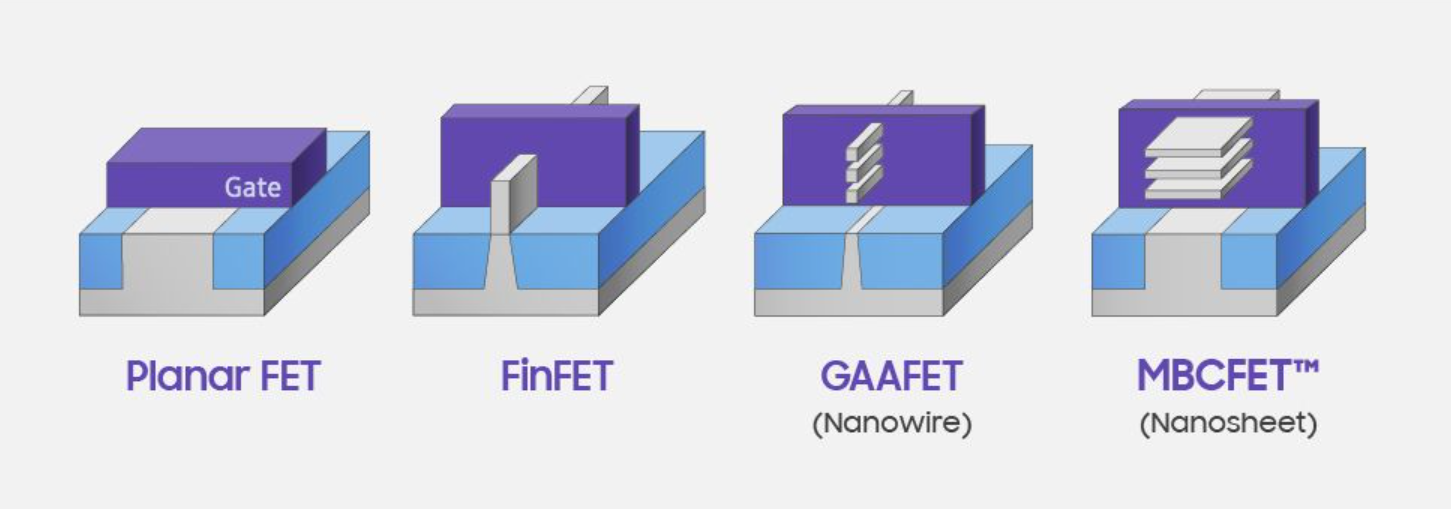

三星的3nm工藝很激進,相比臺積電2nm工藝才會轉向GAA晶體管的保守,三星在第一代3nm工藝上就使用GAA晶體管技術,而且是MBCFET多橋通道場效應晶體管,被稱為SF3E,也就是3GAE工藝。

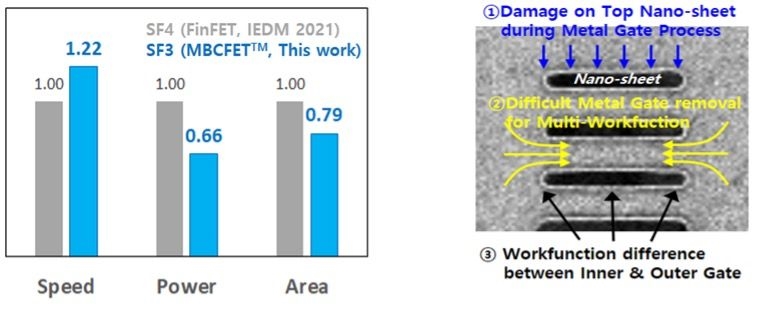

這次宣佈的是SF3工藝,也就是之前的3GAP高性能工藝,三星提到該工藝相比SF4(4nm LPP)工藝,在相同功耗及晶體管密度下速度提升22%,或者功耗降低34%,面積縮小21%。

這個提升幅度很大,但是三星對比的是二代3nm與4nm,沒有直接提及兩代3nm工藝之間的變化。

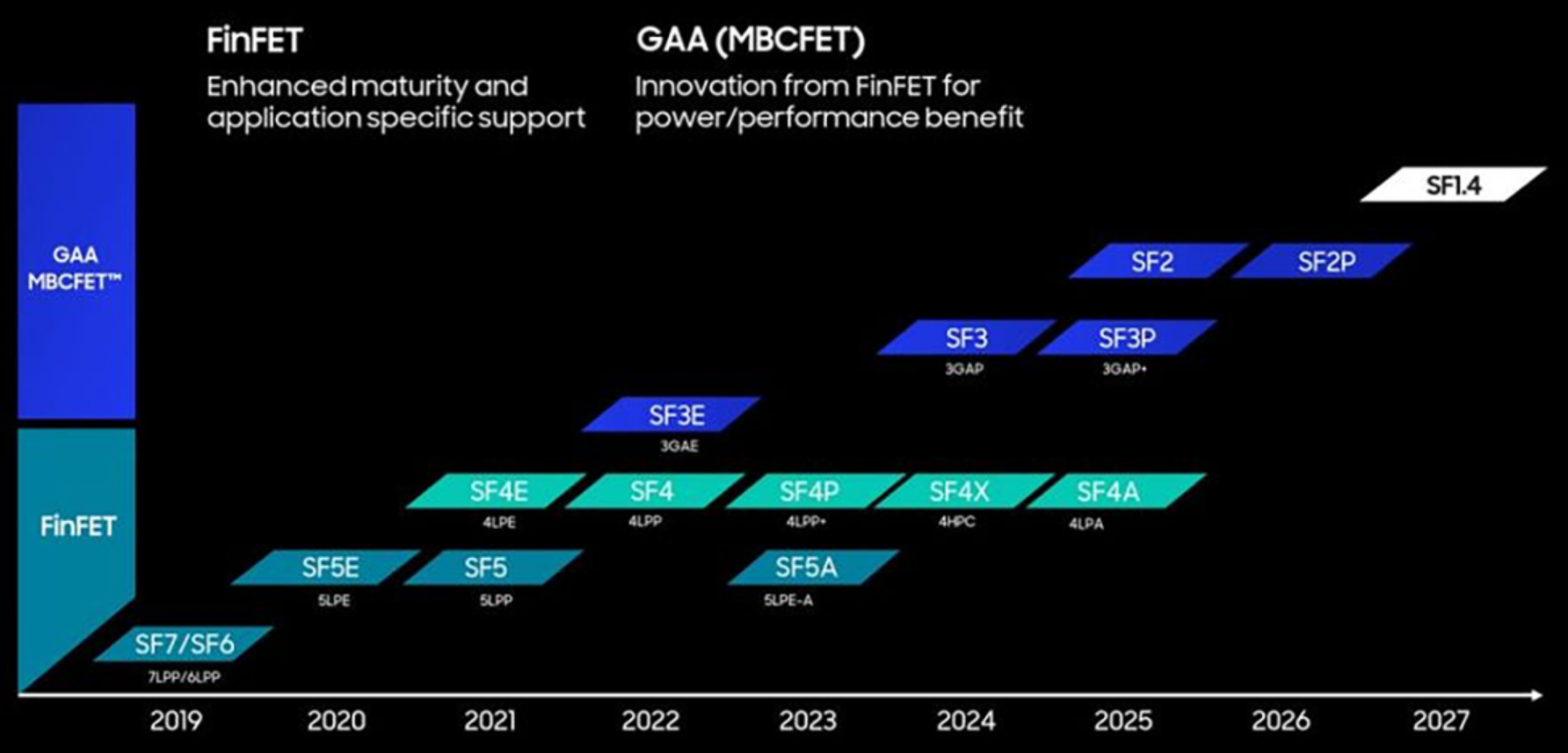

根據三星公佈的路線圖,SF3工藝預計在2024年量產,之後還會有增強版的SF3P,也就是3GAP+,2025年量產。

再往後還有2nm節點的SF2、SF2P工藝,2027年甚至連1.4nm節點的SF1.4工藝也規劃好。