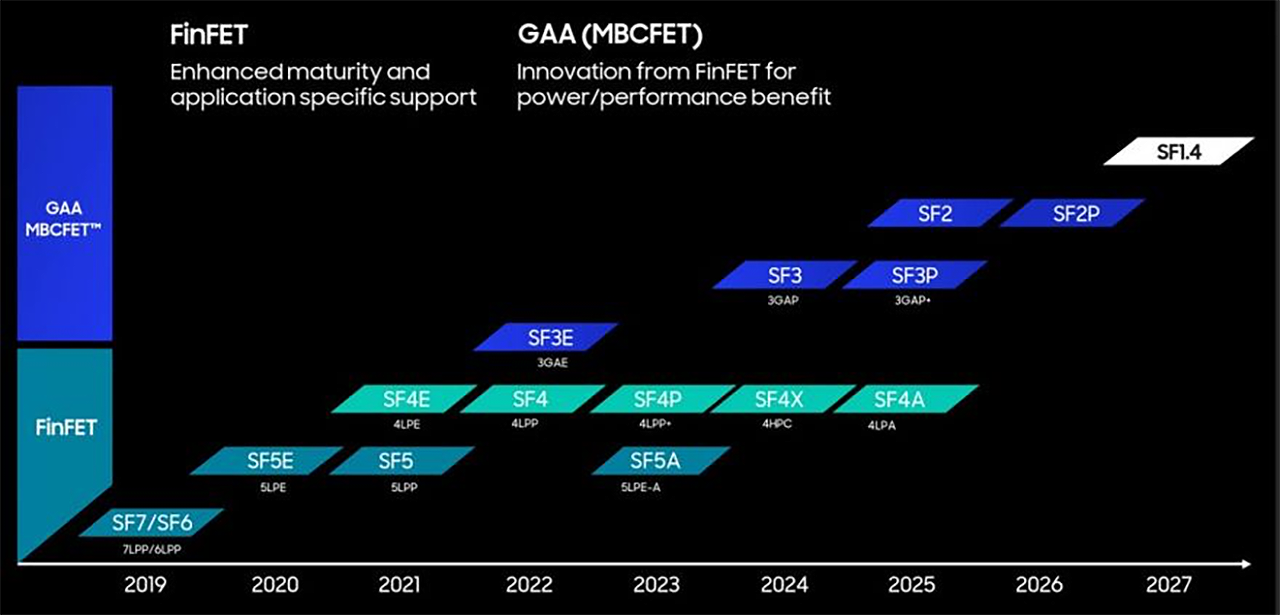

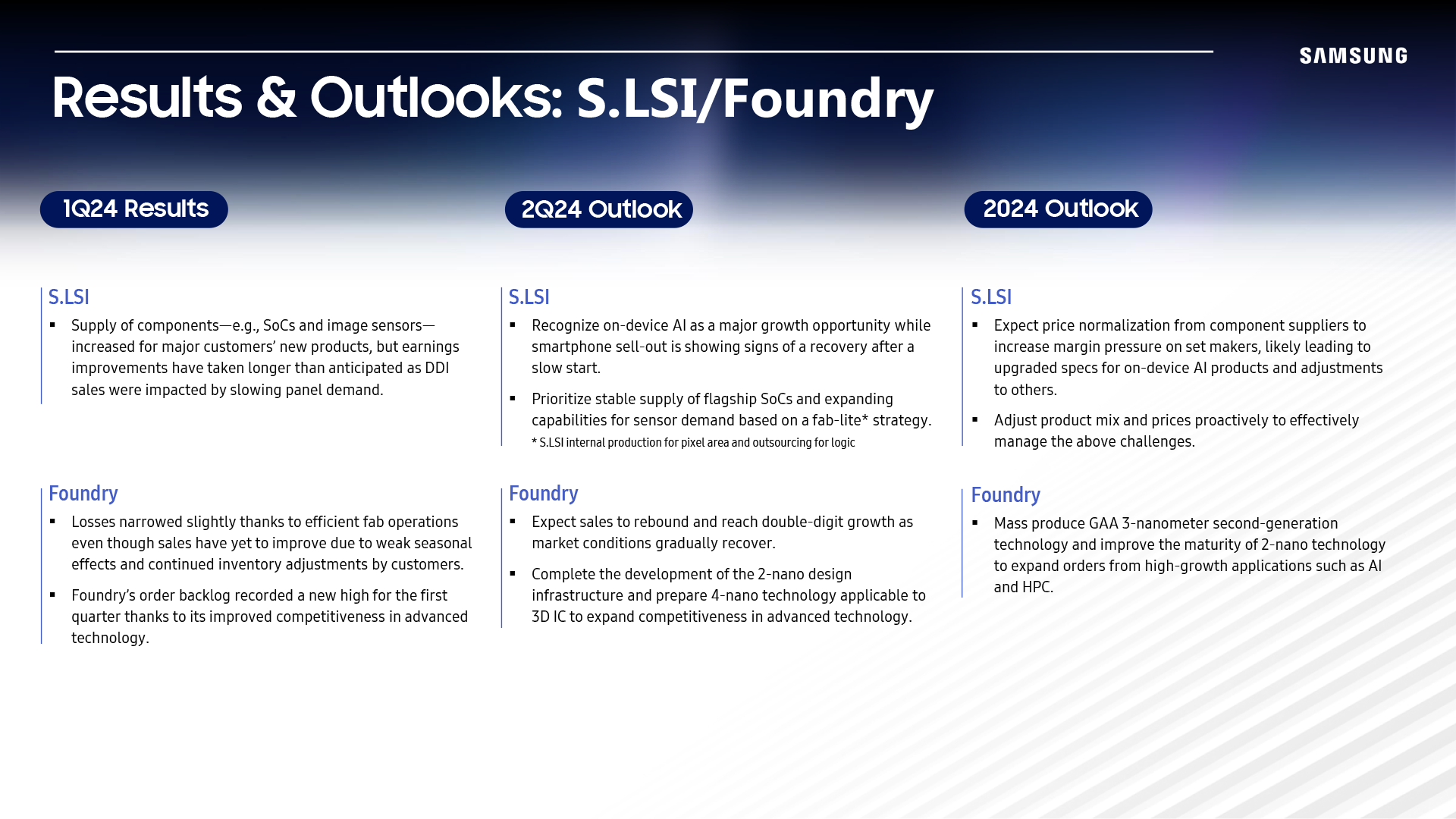

作為三星第一季度財報的一部分,該公司概述其代工部門今年下半年的一些主要計劃。該公司已確認,它仍將如期實現在今年下半年開始量產采用其SF3(3納米級,第二代)技術的芯片的目標。與此同時,三星晶圓代工廠將於6月份正式發佈SF2(2納米級)工藝技術,該技術將提供性能和效率的雙重提升。最後,該公司正在準備將其4納米級技術的變體集成到堆疊3D設計中。

SF2 將於六月亮相

三星計劃在 6 月 19 日舉行的 2024 年超大規模集成電路研討會(VLSI Symposium 2024)上披露其 SF2 制造技術的關鍵細節。這將是該公司基於全柵極(GAA)多橋溝道場效應晶體管(MBCFET)的第二個主要工藝節點。與前代產品相比,SF2 將采用"獨特的外延和集成工藝",這將使該工藝節點比基於 FinFET 的傳統節點具有更高的性能和更低的漏電率(盡管三星並未透露與之比較的具體節點)。

三星表示,SF2 使 N 型和 P 型窄晶體管的性能分別提高 29% 和 46% ,使寬晶體管的性能分別提高 11% 和 23%。此外,與 FinFET 技術相比,它還將晶體管的全局變化減少 26%,並將產品漏電率降低約 50%。該工藝還通過加強與客戶的設計技術合作優化 (DTCO) 為未來的技術進步奠定基礎。

在 SF2 的背景下,三星沒有提到的一點是背面電源傳輸,因此至少目前沒有跡象表明三星將在 SF2 上采用這種下一代電源路由功能。

三星表示,SF2 的設計基礎架構(PDK、EDA 工具和授權 IP)將於 2024 年第二季度完成。一旦完成,三星的芯片開發合作夥伴就可以開始為這一生產節點設計產品。同時,三星已經開始與 Arm 合作,針對 SF2 工藝共同優化 Arm 的 Cortex 內核。

SF3:2024 年下半年有望實現

作為首傢推出基於 GAAFET 節點的工廠,三星一直處於芯片制造的最前沿。但與此同時,這也意味著他們是第一個遇到並解決如此重大的晶體管設計變更所帶來的不可避免的磨合問題的工廠。因此,雖然三星的第一代 SF3E 工藝技術已經投產不到兩年時間,但迄今為止公開披露的采用該工藝制造的芯片都是相對較小的加密貨幣挖礦芯片--這正是在新工藝節點上表現出色的流水線部件。

有這些經驗,三星正準備利用 GAAFET 制作更大更好的芯片。作為其財報公告的一部分,該公司已確認其去年推出的更新 SF3 節點仍將按計劃於 2024 年下半年投入生產。

SF3 從一開始就是一個更加成熟的產品,準備用於制造更大的處理器,包括數據中心產品。與它的前身 SF4 相比,SF3 承諾在相同功耗和晶體管數量下性能提升 22%,或在相同頻率和復雜度下功耗降低 34%,邏輯面積減少 21%。總體而言,三星對這項技術寄予厚望,因為這一代 3nm 級技術有望與臺積電的 N3B 和 N3E 節點相抗衡。

SF4:準備進行 3D 堆疊

最後,三星還在準備將其最終 FinFET 技術節點 SF4 的一個變體用於 3D 芯片堆疊。隨著晶體管密度的提高不斷放緩,三維芯片堆疊已成為不斷提高整體芯片性能的一種方法,尤其是在現代多層處理器設計中。

有關該節點的詳細信息還很有限,但三星似乎正在做出一些改變,以考慮/優化在三維堆疊設計中使用 SF4 芯片的情況,在這種設計中,芯片需要能夠上下層通信。根據該公司的第一季度財務報告,三星預計將在本季度(第二季度)完成堆疊芯片 SF4 變體的準備工作。