臺積電於4月末在美國加利福尼亞州舉辦2024年北美技術論壇,發佈其最新半導體制程技術A16(1.6nm)、下一代先進封裝和3D芯片技術等6大半導體技術創新,引發業界關註。在全球發展人工智能(AI)的熱潮之下,臺積電憑借其領先的芯片技術、穩定擴增的產能,成為英偉達等AI芯片的最重要代工廠。

研究機構TechInsights報告顯示,臺積電2023年總銷售額達到692.76億美元,成為全球半導體產業冠軍。摩根大通(小摩)、摩根士丹利等金融服務機構均對臺積電的後續發展給出樂觀預測,小摩在最新報告中認為,臺積電在技術創新和先進封裝領域的領先地位,以及在AI時代的關鍵作用,通過一系列技術突破,有望在未來幾年繼續保持在半導體產業的領先地位。

以下為臺積電在2024北美論壇公佈的六大半導體技術:

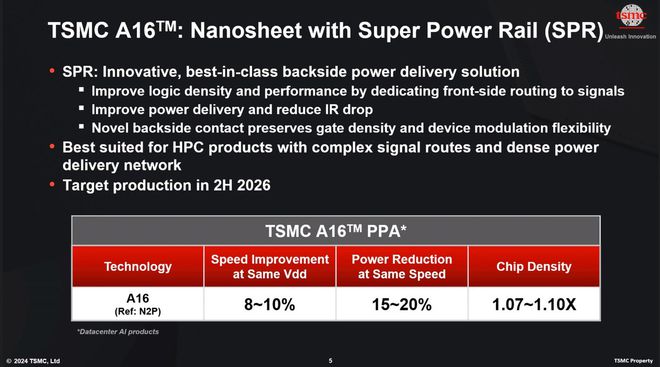

A16 1.6nm制程技術

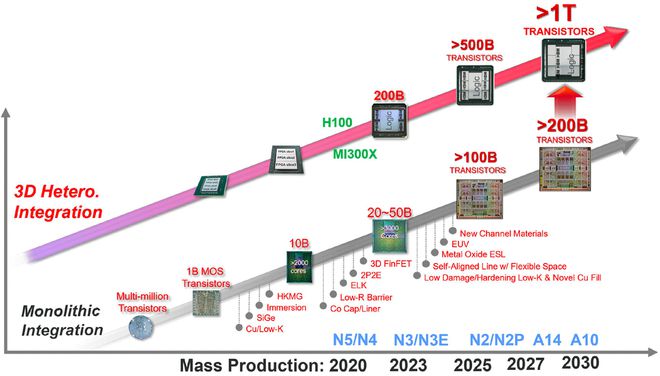

臺積電A16制程節點是其首個整合納米片晶體管(nanosheet)以及背面供電技術“Super Power Rail”的節點,特別適合高性能計算(HPC)及人工智能(AI)應用,是臺積電N2P制程的迭代。根據臺積電此前公佈的路線圖,N2、N2P 2nm節點定於2025年量產,A16預計將於2026年下半年量產。

與2nm N2P節點相比,A16提高晶體管密度和能效,在相同Vdd(正電源電壓)下可實現8~10%的速度提升;在相同速度下,功耗可以降低15~20%。該技術可以幫助數據中心計算芯片實現1.07~1.10倍的芯片密度。

臺積電在北美峰會同時宣佈A14工藝節點,預計將采用第二代納米片晶體管以及更先進的背面供電網絡,有望在2027~2028年開始生產,預計不會采用High NA EUV光刻機。

根據路線圖,臺積電1nm制程A10已在規劃中。消息人士於2024年1月透露,臺積電將更先進制程的1nm晶圓廠規劃在嘉義科學園區,已派人前往目標地塊勘測。這一選址離嘉義高鐵站車程僅七分鐘,往北串起臺積電中科、竹科廠,往南串連南科廠及高雄廠,便於工程師通勤交流。

NanoFlex創新納米片晶體管

臺積電即將推出的N2制程工藝將采用NanoFlex創新納米片晶體管技術,這是該公司在設計與技術協同優化方面的又一突破。NanoFlex為N2制程標準單元提供設計靈活性,其中短小晶體管單元可實現更小的面積和更高能效,而高單元則最大限度提高性能。

客戶能夠在同一設計內優化小單元和大單元的組合,調整設計,以達到最佳功耗、性能和面積平衡。

N4C制程技術

臺積電宣佈推出N4C技術,是N4P的迭代,可降低8.5%的芯片成本,計劃於2025年量產。該技術提供具有高效面積利用率的基礎IP和設計規則,與廣泛應用的N4P兼容,縮小芯片尺寸並提高良率,為客戶提供高性價比選擇。

CoWoS、SoIC和系統級晶圓(TSMC-SoW)

臺積電表示,CoWoS先進封裝已成為AI芯片的關鍵技術,被廣泛采用,允許客戶將更多的處理器內核與HBM高帶寬存儲堆疊封裝在一起。

與此同時,集成芯片系統(SoIC)已成為三維芯片堆疊的領先解決方案,客戶正越來越多地將CoWoS與SoIC及其他組件搭配使用,以實現最終的系統級封裝(SiP)集成。

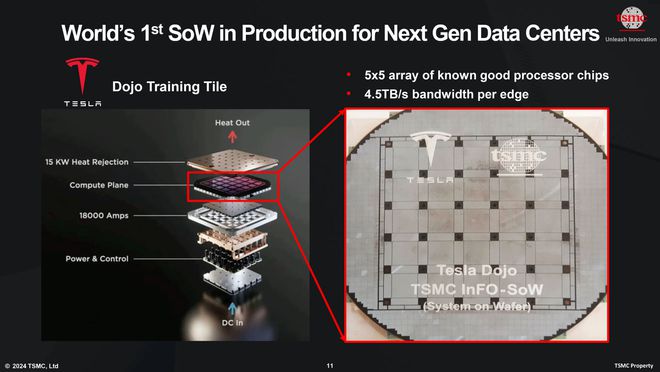

臺積電宣佈推出CoW-SoW封裝技術(TSMC-SoW),基於臺積電於2020年推出的InFO-SoW晶圓上系統集成技術迭代而成。通過晶圓級系統集成封裝技術(SoW),可以在單片12英寸晶圓上制造大型芯片陣列,提供更強算力的同時,減少空間占用,並將每瓦性能提升多個數量級。此前特斯拉的Dojo D1超級芯片,就利用臺積電的此類工藝實現,利用單片晶圓實現強大算力。

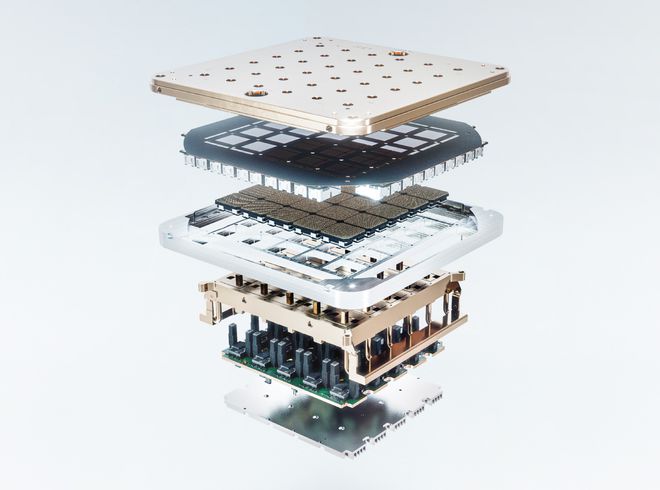

據悉,特斯拉自研的Dojo D1超級芯片采用臺積電7nm制程,並結合InFO-SoW先進封裝、垂直供電結構制造而成,用於訓練自動駕駛汽車AI大模型。參數方面,每個模組包含5×5總計25顆芯片,每個單芯片包含高達354個核心,因此片上SRAM換從總計達11GB,算力9050TFLOPS。

臺積電表示,首款SoW產品——基於集成扇出型封裝(InFO)技術的純邏輯晶圓已投入生產。利用CoWoS技術的CoW-SoW晶圓預計將於2027年問世,屆時將可以集成SoIC、HBM和其他組件,創建強大的單晶圓級系統,其計算能力可以與整個機架甚至整個服務器相媲美。這類芯片將擁有巨大的面積,可以集成四個SoIC芯片+12個HBM存儲芯片以及額外的I/O芯片,功率可達數千瓦。

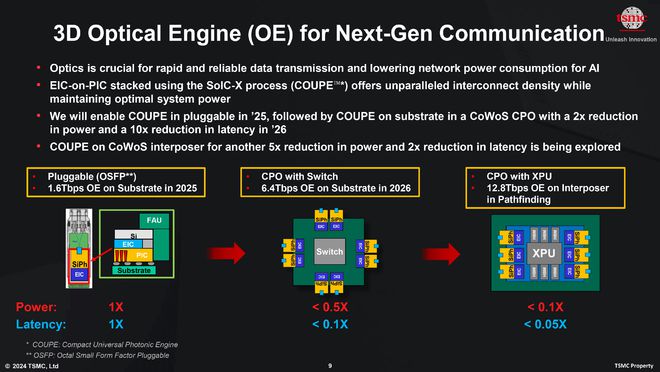

矽光子集成COUPE

臺積電正在開發緊湊型通用光子引擎(COUPE)技術,以支持人工智能熱潮帶來的數據傳輸爆發式增長。COUPE采用SoIC-X芯片堆疊技術,在矽光子芯片堆疊電子芯片,並保證兩片芯片之間最低的傳輸阻抗,能效比傳統堆疊方式更高。

臺積電計劃在2025年將COUPE技術用於小尺寸插拔式設備,速度可達1.6Tbps,相比當前最先進的800G以太網成倍提升。2026年,臺積電將其整合入CoWoS封裝中,作為共同封裝光學器件(CPO)直接將光學連接引入封裝中,這樣可以實現高達6.4Tbps的速度。第三個迭代版本有望進一步改進,速度翻倍至12.8Tbps。

汽車芯片先進封裝

繼2023年推出N3AE“Auto Early”制程後,臺積電將繼續通過整合先進芯片和先進封裝,滿足汽車客戶對更高算力的需求,以及車規級認證的要求。臺積電正在為高級輔助駕駛系統(ADAS)、車輛控制和車載中央計算機等應用開發InFO-oS和CoWoS-R解決方案,目標是在2025年第四季度之前獲得AEC-Q100 2級認證。

日前臺積電法說會之後,大摩預計臺積電Q2營收將環比增長5%~7%,並給出860元新臺幣的目標股價預測。小摩預測臺積電今年毛利率維持在52%~54%區間,預計今年年底3nm產能將達到10萬片規模,明年將增加到15萬片,並給出900元新臺幣的目標股價。小摩同時預計,臺積電在未來3~4年內,在AI芯片的市場占有率仍將維持在90%以上,到2027年AI相關收入占比將升至總營收的25%。

臺積電法說會、多場技術論壇過後,給市場釋出穩健信號,包括花旗銀行、美銀證券、瑞銀在內的金融機構,均對臺積電給出全年營收增長的預測。在人工智能市場需求持續增長的帶動下,以及美日芯片工廠新產能的釋放,預計臺積電未來幾年將持續領銜全球半導體產業,並憑借技術實力保持AI芯片領域的龍頭地位。