臺積電最近在加利福尼亞州聖克拉拉舉行瞭年度技術研討會,演講全面概述瞭它們的狀態和即將到來的路線圖(《臺積電最新工藝路線圖,2nm正式亮相》),涵蓋瞭工藝技術和先進封裝開發的各個方面。本文將總結工藝技術更新的亮點。

魏哲傢分享的一些信息

“今年是臺積電成立 35 周年。1987 年我們成立,當時我們一共擁有 258 名員工,並發佈瞭涵蓋 3 種技術的 28 種產品;十年後,我們擁有 5,600 名員工,發佈瞭涵蓋 20 種技術的 915 款產品;到 2022 年,我們有 63,000 名員工,將發佈 12,000 種產品,涵蓋 300 項技術。”

“從 2018 年到 2022 年,12 英寸晶圓(當量)的年復合增長率超過 70%。特別是,我們看到‘big die’產品數量的顯著增加。” (>500mm²)

“2021年,臺積電北美業務板塊出貨量超過700萬片,產品出貨量超過5500件。有 700 個新產品流片 (NTO)。這部分占臺積電收入的 65%。”

“我們的 gigafab 擴張計劃通常包括每年增加兩個新的‘階段’——2017-2019 年就是這種情況。2020 年,我們開設瞭六個新階段,包括我們的先進封裝工廠。2021年有7個新階段,包括臺灣和海外的晶圓廠,也增加瞭先進封裝產能。2022年將有5個新階段,無論是在臺灣還是在海外。”

N2晶圓廠:新竹Fab20

N3:臺南Fab 18

N7和N28:高雄Fab22

N28:中國南京的Fab16

N16、N28 和專業技術:日本熊本的 Fab23(2024 年)

亞利桑那州的 N5(2024 年)

“統計全球已經安裝的EUV光刻機系統中,臺積電擁有瞭其中的 55%”

“我們將在 2022 年大幅擴大資本設備投資。” (下表突出顯示瞭上限設備計劃支出的大幅增長。)

“我們正在經歷成熟工藝節點的制造壓力。35 年來,我們從未在後續節點大規模生產後增加成熟節點的產能——但這種情況正在發生莊邊。我們正在投資以提高我們 45nm 工藝的產能。” (後來,在與另一位臺積電高管的問答環節中,有記者問道是否會在例如 90nm 或 65nm等其他成熟節點上執行產能擴張,他們給出的回應是:“不,擴張計劃目前僅針對 45nm 節點。”)

“我們繼續大力投資‘智能制造’,專註於精密過程控制、工具生產力和質量。每個 gigafab 每天處理 1000 萬個調度訂單,並優化工具生產力。每個 gigafab 每天都會生成 70B 的數據點以進行主動監控。”

在研討會上,首次在展廳分配瞭一個特殊的“創新區”。重點介紹瞭一些初創公司最近提供的產品。臺積電表示:“我們增加瞭支持投資,以幫助小公司采用我們的技術。有一個專門的團隊專註於初創企業。對小客戶的支持一直是重點。也許這個領域的某個地方將成為下一個英偉達。”

臺積電的 12 個關鍵裡程碑

1987 年,隨著 PurePlay 商業模式的創建,臺積電成立。

1999 年,臺積電成為第一傢提供 0.18 微米銅技術的代工廠。

2001 年帶來瞭第一個代工參考設計流程。臺積電花費瞭大量資金來創建我們今天享有的龐大 EDA 和 IP 生態系統。

2011 年,臺積電將 HKMG 28nm 帶入無晶圓生態系統。其他代工廠在 28nm 時步履蹣跚,因此這是臺積電創紀錄的節點。

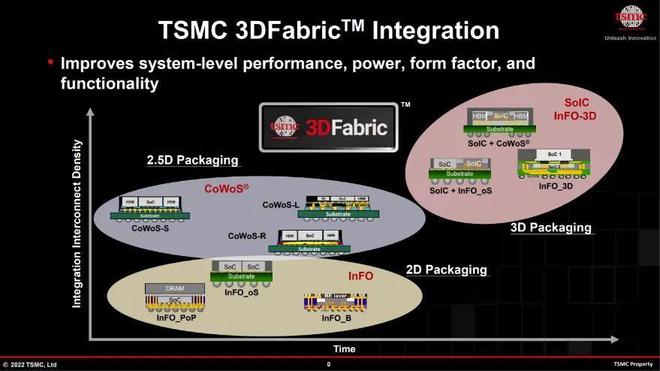

2012 年推出瞭CoWos,第一款異構 3DIC test vehicle 。

2014 年,臺積電交付瞭第一款功能齊全的 FinFET 網絡處理器,開啟瞭今天臺積電主導的 FinFET 時代。

2015 年臺積電通過瞭先進的 3DIC 封裝技術 InFo。

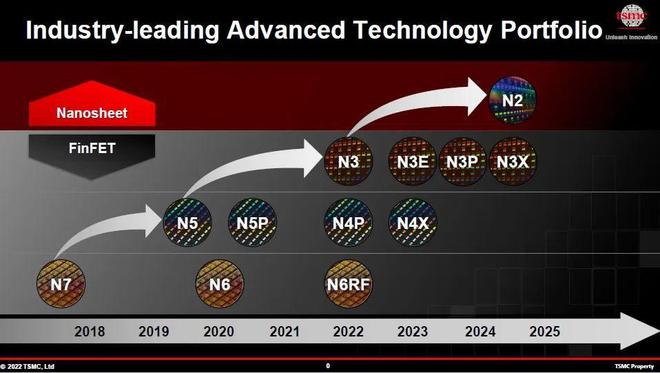

2018 年,臺積電向所有人提供瞭最先進的邏輯技術 (N7)。

2020 年,臺積電以基於 N5 EUV 的邏輯技術引領行業。

2021 年,臺積電推出 N4P、N4X 和 N6RF。

2022 年,臺積電將推出覆蓋廣泛垂直市場的最先進的 N3 工藝節點。我認為 N3 也將在 5 年內打破流片記錄。

最後但同樣重要的是,臺積電在 2022 年宣佈瞭面向大眾的下一代工藝技術 (N2)。

工藝技術回顧

除瞭進一步討論的一些例外情況外,支撐技術路線圖演示有些例行公事——這不是一件壞事,而是表明正在成功執行先前的路線圖。

路線圖更新被提出瞭兩次,一次是作為技術議程的一部分,另一次是作為臺積電平臺解決方案重點的一部分。回想一下,臺積電特別確定瞭四個“平臺”,它們分別接受開發投資以優化工藝技術產品,當中包括:移動;高性能計算(HPC);汽車;和物聯網(超低功耗)。下面的摘要合並瞭兩個演示文稿。

N7/N6

到 2022 年底,超過 400 個 NTO,主要在智能手機和 CPU 市場

N6 提供從 N7 的透明遷移,支持 IP 重用

N6RF 將成為即將推出的 WiFi 7 產品的射頻解決方案

有一個 N7HPC 變體(上圖中未顯示),在overdrive VDD 電平下提供約 10% 的性能提升

對於 N6,基於邏輯單元的模塊可以在新庫中重新實現,以進一步提高性能,實現主要的邏輯密度提高 (~18%)。

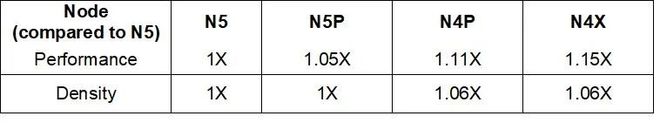

N5/N4

在生產的第 3 年,使用這個工藝的晶圓出貨量超過 200 萬片,到 2022 年底將達到 150 個 NTO

移動客戶是第一位的,其次是 HPC 產品

路線圖包括正在進行的 N4制程增強

N4P 基礎 IP 已準備就緒,接口 IP 在 2022 年第三季度可用(到 v1.0 PDK)

有一個 N5HPC 變體(上圖中未顯示,性能提升約 8%,HVM 將在 2H22)

N3 和 N3E

N3 將於 2022 年下半年開始進入 HVM

一年後大規模量產N3E 工藝變體;臺積電期望該工藝在移動和 HPC 平臺上得到廣泛采用

N3E 已準備好開始設計(v0.9 PDK),在標準 256Mb 存儲器陣列鑒定測試現場具有高良率

N3E 添加瞭“FinFLEX”方法選項,三個不同的單元庫針對不同的 PPA 要求進行瞭優化

請註意,N3 和 N3E 與之前的臺積電工藝路線圖有些反常。N3E 不會提供從 N3 透明遷移的 IP。N3E 產品有點“修正”,因為采用瞭對 N3 的重大設計規則更改來提高良率。

臺積電的早期采用者客戶在積極的時間表上推動工藝 PPA 更新,無論是對現有基線(例如,N7 到 N6、N5 到 N4)的增量兼容變體,還是新節點。最初的 N3 流程定義具有良好的 NTO pipeline,但 N3E 將成為未來變體的基礎。

N2

基於納米片技術,目標生產日期:2025

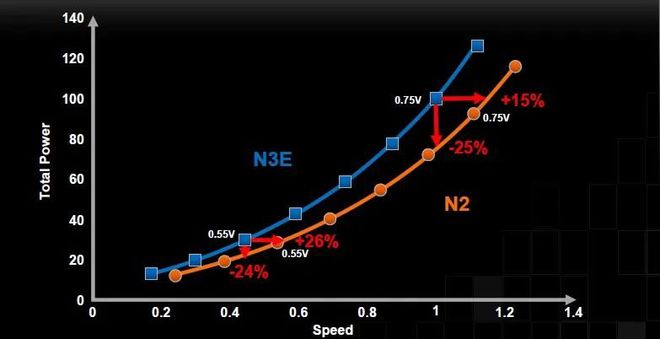

與 N3E 相比,N2 將提供約 10-15% 的性能提升(@iso-power,0.75V)或約 25-30% 的工號降低(@iso-perf,0.75V);另請註意上圖中指定的工作范圍低至 0.55V

N2 將為後端配電網絡提供支持

順便說一句,臺積電面臨兩難境地,即不同平臺的要求具有如此廣泛的功耗、性能和面積/成本目標。如上所述,N3E 正在使用不同的庫解決這些問題,並結合瞭定義單元高度的,不同數量的鰭。對於 N2 庫設計,該設計決策被關於整個垂直堆疊納米片數量的工藝技術決策所取代(器件納米片寬度有一些允許的變化)。就納米片拓撲而言,看看臺積電選擇為 N2 提供什麼來覆蓋移動和 HPC 市場將會很有趣。(下圖來自臺積電在 VLSI 2022 大會上的早期技術演示,描繪瞭 3 個納米片。)

註意:有兩種新興的工藝技術正在被采用來降低功率傳輸阻抗和改善局部可佈線性——即“埋地”電源軌 (BPR:buried power rail) 和“背面”配電 (BSPDN:backside power distribution)。對提供 BPR 的初步調查已迅速擴展到處理集成完整 BSPDN(如 N2)的路線圖。然而,很容易混淆這兩個首字母縮寫詞。

有關特殊工藝的分享

臺積電將以下產品定義為“Specialty Technologies”(專業技術)類別:

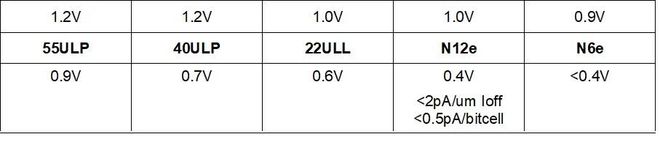

一、超低功耗/超低泄漏(使用超高 Vt 器件變體)

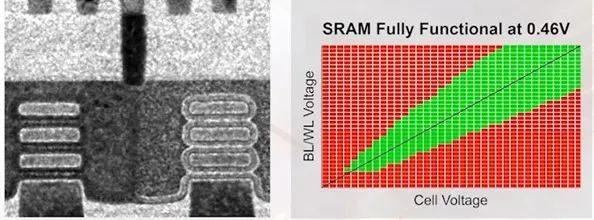

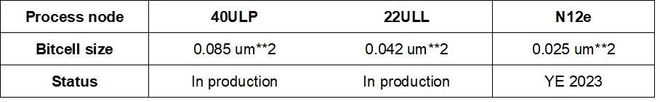

需要特別關註超低泄漏 SRAM 位單元設計

N12e 在生產中,N6e 在開發中(專註於極低 VDD 型號支持)

二、(嵌入式)非易失性存儲器

1、通常與微控制器 (MCU) 集成,通常在 ULP/ULL 過程中

2、RRAM

需要 2 個額外的掩膜,嵌入 BEOL中(比 eFlash 的 12 個掩膜成本低得多)

10K 寫入周期(耐久性規格),在 125C 時保持約 10 年

3、MRAM

22MRAM已經量產,重點是提高耐受度

2023 年量產面向Automotive Grade 1應用的 16MRAM

三、電源管理 IC (PMIC)

基於雙極 CMOS-DMOS (BCD) 器件:40BCD+、22BCD+

適用於復雜的 48V/12V 電源域

需要極低的設備 R_on

四、高壓應用(例如,顯示驅動器,使用 N80HV 或 N55HV)

五、模擬/混合信號應用,需要獨特的有源和無源結構(例如,使用 N22ULL和 N16FFC 的精密薄膜電阻器和低噪聲器件)

六、MEMS(用於運動傳感器、壓力傳感器)

七、CMOS 圖像傳感器(CIS)

N65 像素大小為 1.75um,N28 像素大小為 0.5um,過渡到 N12FFC

八、射頻 (RF),從毫米波到更長波長的無線通信;即將推出的 WiFi7 標準被強調

“從 WiFi6 到 WiFi7 的過渡將需要顯著增加面積和功率,以支持增加的帶寬要求——例如,2.2X 面積和 2.1X 工號。臺積電正在對 N6RF 產品進行認證,與 N16RF 相比,功耗降低瞭約 30-40%。這將允許當前使用 N16RF 的客戶在開發 WiFi7 設計時大致維持現有的功率/面積目標。”

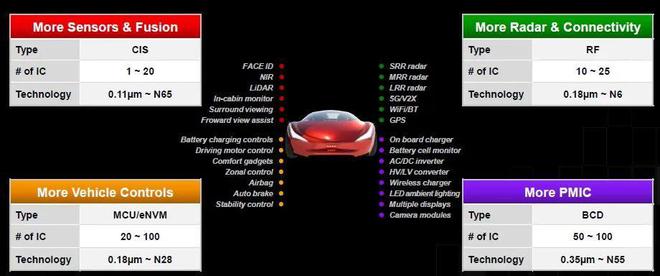

下圖說明瞭這些專業技術如何成為平臺產品(例如智能手機和汽車產品)的基本組成部分。還顯示瞭用於這些應用程序的特征過程節點。

盡管智能手機開發的重點往往集中在主應用處理器上,但下表突出瞭對專業技術產品及其相關功能的極其多樣化的要求。在汽車領域,向“區域控制”架構的過渡將需要一套新的汽車 IC。

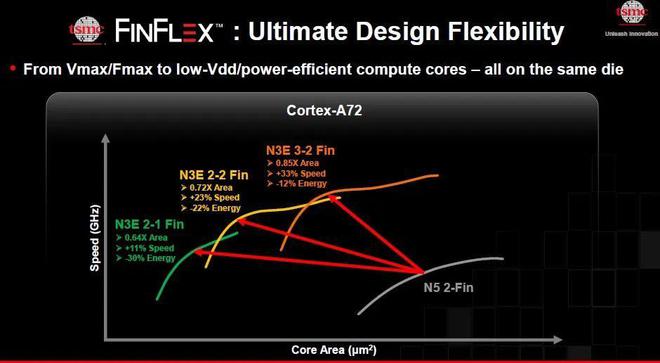

N3E 和 FinFLEX

臺積電特別強調瞭新發佈的 FinFLEX 方法,臺積電表示,FinFLEX 將提供 N5 的全節點擴展。

隨著 FinFET 技術節點的擴展(即從 N16 到 N10 到 N7 到 N5), fin profile和驅動電流每微米顯著改善。標準單元庫(Standard cell library)設計已發展為包含更少的 pFET 和 nFET 鰭,這些鰭定義瞭單元高度(根據水平金屬佈線軌道的數量指定)。如上圖所示,N5 庫使用 2-2 鰭定義——即 2 個 pFET 鰭和 2 個 nFET 鰭來定義單元高度。(N16/N12 使用 3-3 配置。)

N3E 的庫定義面臨幾個問題。pFET 和 nFET 器件性能改進的規模並不相同。而且,就其 PPA(和成本)目標而言,移動和 HPC 平臺應用程序的差異越來越大。移動產品專註於電路密度,以集成更多功能和/或降低功耗,同時對性能改進的要求不高。HPC 更專註於最大化性能。

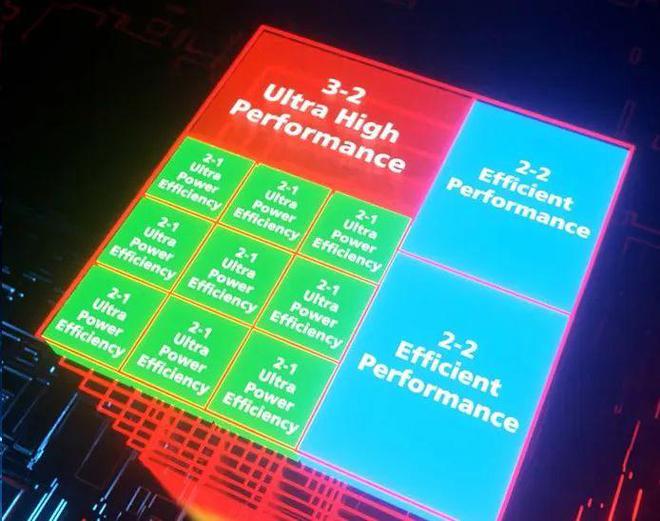

因此,N3E 將提供三個庫,如上圖所示:

2:1超低功耗庫(軌道高度由 2 pFET:1 nFET 定義)

2:2高效庫

3:2性能庫

下圖來自臺積電的 FinFLEX 網站,說明瞭這個概念。

現在,在單個 SoC 上集成多個庫並不是什麼新鮮事。多年來,處理器公司開發瞭獨特的“datapath”和“control logic”庫產品,針對不同的目標:單元高度、電路性能、可佈線性(即最大單元面積利用率)和不同的邏輯產品(例如,寬 AND-用於數據路徑多路復用的或門)。然而,使用多個庫的 SoC 設計的物理實現依賴於每個設計塊的一致庫。

盡管上面的 TSMC 圖片還描繪瞭每個塊(block)一個庫,但 FinFLEX 方法的獨特性在於多個庫和多個軌道高度將在一個塊中混合。 將支持 2:1 加 2:2 庫和 2:2 加 3:2 庫組合。

臺積電表示, “在一個塊中啟用不同的單元高度(在單獨的行中)以優化 PPA。N3E 中的 FinFLEX 結合瞭新的設計規則、新的佈局技術以及對 EDA 實施流程的重大更改。”

肯定會有更多關於 FinFLEX 和一般設計流程變化的信息。另一方面,需要有新的方法來:

一、floorplanning

為一個block規劃兩種不同行高的百分比組合

不同庫行中單元的目標利用率百分比以實現可佈線性(包括用於decap fill的 open cells)

對於具有顯著百分比的低功率單元的塊的 PDN“減少”方法

block的佈局規劃迭代次數(通過物理綜合)以達到閉合

二、physical synthesis

合成將如何改善關鍵信號的時序

為瞭改善高負載信號的時序,綜合通常會將庫中的單元分配更新為下一個更高的驅動強度——例如,NAND2_1X 到 NAND2_2X。

對於 FinFLEX,第二個庫提供瞭其他選項——例如,對 NAND2_1X_2:2 的更新是使用 NAND2_2X_2:2 還是 NAND2_1X_3:2。然而,如果選擇後者,則需要將新單元“重新平衡”到塊平面圖中的不同行。這些選擇的性能和輸入/輸出線負載的有效變化在物理綜合期間難以估計(更不用說不同庫單元的輸出上升與下降的特定 RDLY 和 FDLY 延遲轉換可能會不同地縮放)。

考慮到要使用的特定觸發器單元(specific flop cells )時,單元選擇選項變得更加復雜,不僅考慮到clock-to-Q 延遲的差異,還考慮到建立和保持時間特性以及輸入時鐘負載。寄存器中的各個觸發器位在同一庫中使用不同的驅動強度(並放置在本地)與將寄存器位重新平衡到對應於不同庫選擇的行相比,什麼時候會更好?

三、子塊級IP集成

塊通常包含許多小的硬核 IP 宏,例如寄存器文件(通常由寄存器文件生成器提供)。由於跨越單個塊的單元行高度不均勻,這些硬核 IP 宏將如何設計和放置?

四、物理設計期間的時序/功耗優化

與物理綜合模塊構建(physical synthesis block construction)選項類似,在物理設計流程的時序和功率優化步驟中,單元選擇將面臨困難的決定。例如,如果一個單元可以降低其分配的驅動強度以節省功耗,同時仍然滿足時序,是否會考慮改變庫選擇,從而重新平衡行?單元格位置的變化會否定優化嗎?

五、最後但最重要的是,啟用 N3E FinFLEX 是否會產生新的 EDA 許可費用?

(幾年前,我以前雇主的 CAD 部門經理在許可證成本加法器上大行其道,以實現多模式要求的佈局和佈線。鑒於支持 FinFLEX 所需的大量 EDA 投資,歷史可能會重演,增加許可證功能成本.)

FinFLEX 方法無疑提供瞭一些有趣的選項。看看這種方法如何演變將非常有趣。

模擬設計遷移自動化

最後,臺積電簡要強調瞭他們在協助設計人員將模擬/混合信號電路和佈局遷移到更新的工藝節點方面正在進行的工作。

具體來說,臺積電定義瞭一組“模擬單元”,能夠采用現有原理圖、重新映射到新節點、評估電路優化和遷移佈局,包括自動佈局和(PG + 信號)佈線。

N5/N4 和 N3E 的模擬單元庫的定義已經完成,後續支持 N7/N6。TSMC 展示瞭一個通過遷移流程的運算跨導放大器 (OTA) 示例。