從7nm到5nm,從5nm到3nm,半導體產業對於先進工藝制程的追求永不停歇。2022年,當臺積電宣佈已經掌握成功大量量產3nm鰭式場效電晶體制程技術後,1nm開始一步步逼近。對於先進工藝的掌握,意味著更高的性能、更頂尖的技術。從3nm跨越到1nm,這其中面臨的技術挑戰猶如天塹。因此,1nm對於業界來說也充滿著誘惑。

01

1nm,念念不忘

工藝制成的研發和生產需要大量的資源,一方面是技術積累,如晶體管架構、材料選擇、制造過程等方面都需要解決難題;另一方面還需要強大的資金、人才和設備,眾所周知從5nm走到3nm,生產成本也翻一番。並非人人都有“資格”追求1nm。從28nm跳級到1nm這之間的差距絕對令人望而卻步。

我們來看看,目前有野心追求1nm的機構和企業分別有哪些。

最新的消息是日本計劃與法國合作開發1nm制程半導體。具體來看,是日本芯片制造商 Rapidus、東京大學將與法國半導體研究機構Leti合作,共同開發電路線寬為1nm級的新一代半導體設計的基礎技術。

法國的CEA-Leti成立於1967年,該研究所的前身是成立於1957年的CENG(格勒諾佈爾核研究中心)的電子系。在芯片的發展進程中,CEA-leti的也有很多重要裡程碑事跡,如其是推動矽上絕緣體場效應管(FD-SOI)技術的重要推動者之一。

日本芯片制造商Rapidus大傢應該不陌生。這傢企業成立的時間非常晚——2022年8月,其集合日本的8傢企業和日本政府提供的700億日元資金。一成立的目標就是,要在4年內量產2nm芯片。當時與IBM建立戰略合作關系,向著2nm進發。不過目前,日本國內最先進的制程還停留在45nm。所以日本能否通過這次“豪賭”,從45nm跨越到2nm是業界還在期待的事。

現在看來,日本的野心並不僅僅止步於2nm,其也想朝著1nm的目標前進。合作方式是 Rapidus與東京大學、Leti研究所進行一些涉及的人員交流和基礎研究共享。Leti 將探索新型晶體管結構,而Rapidus和其他日本合作夥伴將派出科學傢,然後評估和測試原型。

IBM在2021年就推出全球首款2nm芯片,使用GAA環繞柵極晶體管技術,一時震動業界。從歷史上看,從5nm走到2nm,IBM使用不到四年。在2nm之後,IBM自然而然的走向1nm。在2022年末的 IEDM 會議上,IBM展示其為通向1nm及以上準備的技術:互連3.0和VTFET。

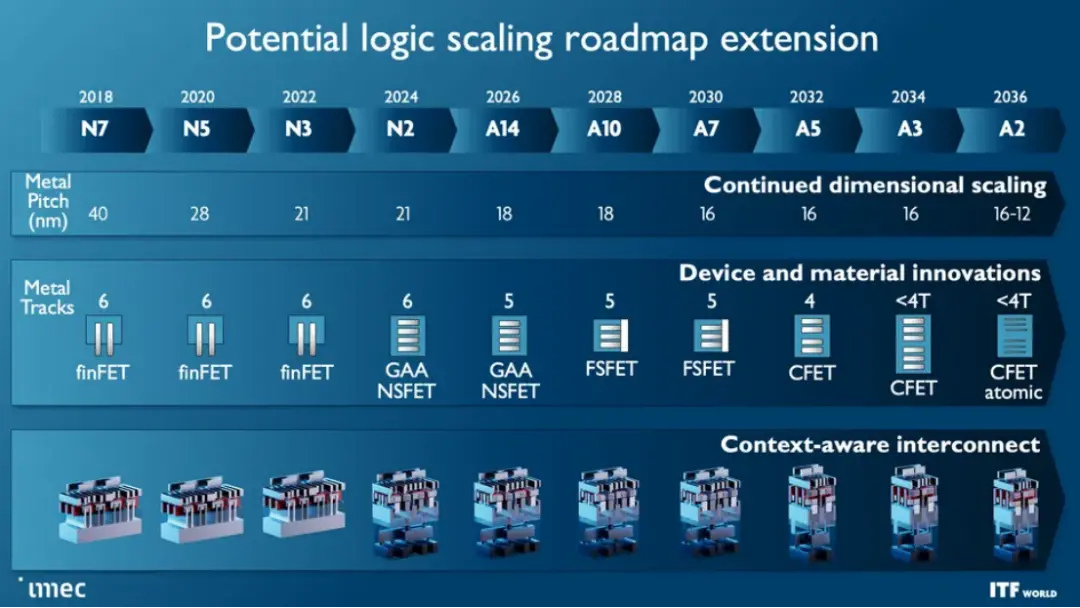

Imec在今年5月公佈1nm以下晶體管的路線圖,在其路線圖中1nm等於10埃。不僅如此,到6月,Imec更是表示其與ASML簽署一項重要協議,與ASML共同合作開發1nm以下芯片。ASML將提供最新型號 0.55 NA EUV、2nm 和 1nm 工藝開發關鍵的 TWINSCAN EXE:5200,以及最新型號 0.33 NA EUV TWINSCAN NXE:3800。

企業方面,作為目前唯一一傢能夠成功實現3nm量產的晶圓廠,臺積電也早早開始研究1nm。臺積電已經選定其1nm新廠的落腳位置,在竹科龍潭園區。從進展上來看,若一切順利,竹科龍潭園區三期2026年中即可供廠商展開建廠作業,這也意味著臺積電1nm廠最快能夠在2026年動工,2027年試產,2028年量產。實際上,這也符合Imec預測的1nm以下路線圖。

來源:IMEC

芯片龍頭英特爾對於1nm的誘惑同樣無法抗拒。從工藝節點來看,英特爾目前準備將Intel 4,用於Meteor Lake處理器和Granite Rapids,下一步將是Intel 3,它將使用EUV光刻來實現更大的模塊化,PPW增加到18%。而英特爾最新的工藝是20A和18A。Intel 20A本來被稱為Intel 1,但是由於英特爾想要“更好的喚起下一個創新時代”,將其命名為20A 。

現在問題來:1nm未來,如何實現?

02

2D材料

尋找合適的晶體管結構以及合適的晶體管材料來實現 1 納米工藝幾何結構的工作仍然是一個好的方向。使用非矽材料有利於制造非常微小的晶體管——小至 1 納米。

2019年時,IMEC就在IEEE會議上,展示2D材料可實現1nm以下的工藝節點。當時IMEC已經展示具有微小特征尺寸的二硫化鉬 (MoS2) MOSFET可以為晶體管的極端縮放開辟途徑,遠低於矽器件短溝道效應的水平。

MoS2是一種二維材料,這意味著它可以以穩定的形式生長,厚度僅為一個原子,最重要的是,在該尺度上具有原子精度。

麻省理工學院、南洋理工大學和臺積電的研究人員發現,二維材料與半金屬鉍 (Bi) 結合可實現極低的電阻,克服實現 1 納米芯片的挑戰。

臺積電也同樣宣佈,其在2D材料方面取得突破,逼近1 nm。在2022年時,臺積電和麻省理工學院、南洋理工大學聯合發表一篇論文,描述金屬引起的導電間隙帶來的制造挑戰,以及單層技術如何受到這些金屬引起的間隙的影響。

這篇文章中建議使用後過渡金屬鉍和一些半導體單層過渡金屬二硫族化物來減小間隙的尺寸,從而生產出比以前小得多的2D晶體管。在實驗中,臺積電嘗試目前各種低電阻的半導體材料,二硫化鉬(MoS2)、二硫化鎢(WS2)和二硒化鎢(WSe2)。

03

改變銅 (Cu) 互連

在計算機芯片之中,半導體組件之間的佈線被稱為互連。簡單解釋,互連就是電流在芯片中各個晶體管、存儲器、處理單元和其他組件之間的流動方式,如果互連的傳輸越有效,那麼芯片的效率就會越高。

在1997年以前,大傢往往都在使用鋁互連。之後,IBM又發現更有效的銅互連。銅線的導電電阻比鋁線低約 40%,這意味著處理速度提高約 15%。在過去的幾十年裡,這種巨大的轉變導致銅成為互連的行業標準。

現在,銅互連也開始遇到瓶頸。銅互連始終需要阻擋襯裡材料來形成適當的佈線結構。隨著器件縮小,可用於銅佈線和襯墊材料的空間變得更小。

目前業界一直在尋找其他金屬可以替代銅互連。

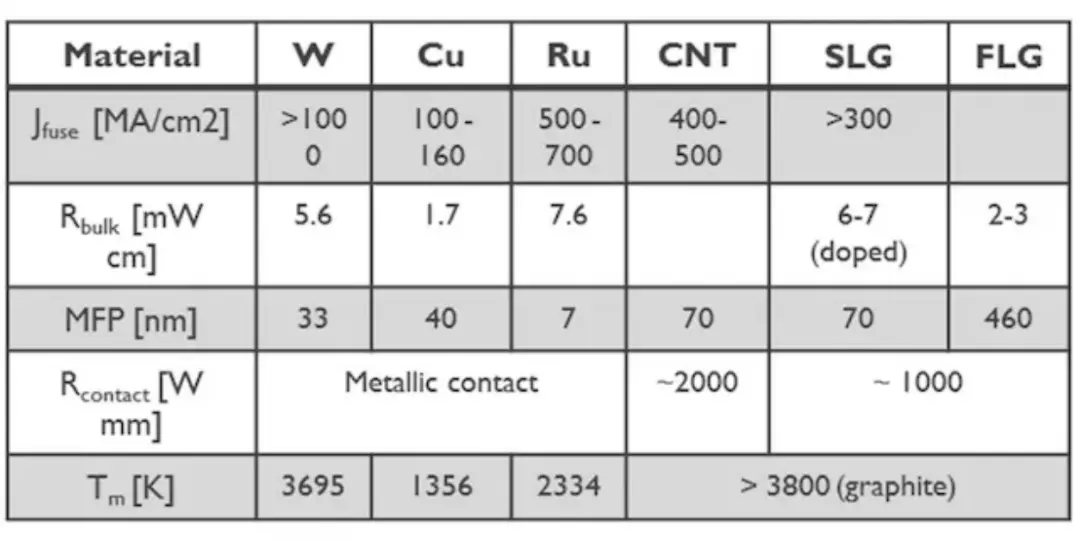

碳納米管 (CNT)、單層石墨烯 (SLG) 和少層石墨烯 (FLG))與其他相關互連材料(鎢 (W)、銅 (Cu) 和釕 (Ru))的性能比較 來源:IMEC

IBM:使用釕

IBM找的方式是使用釕。釕可以擴展到 1 納米及以上節點,並且仍然是一種有效的導體,因此不需要襯墊,這有助於節省空間。通過減色圖案化方法形成的釕也有可能用於一種新型互連集成方案,稱為頂通孔集成。在這種情況下,互連通孔形成在導線的頂部,而不是導線的下方,從而允許為最關鍵的互連層形成連續的導線和自對準通孔。此外,通過這種頂通孔集成牢固地形成嵌入式氣隙,從而減少互連寄生電容,也將有助於實現更快、更低功耗的芯片。IBM的研究人員使用極紫外光刻 (EUV) 雙圖案現有的機器上創建測試結構,結果表明能夠實現突破。

IMEC、臺積電:使用石墨烯

與IBM的方式不同,臺積電嘗試使用石墨烯進行多層佈線。

人們對石墨烯互連應用的興趣並不令人意外。石墨烯表現出高本征載流子遷移率(高達200,000cm2 V -1 s -1)和大載流能力(高達108A/cm2)。此外,石墨烯具有高導熱性和抗電遷移的競爭穩健性。它還可以制成原子級厚度,這有助於減輕厚度對 RC 延遲的影響。

臺積電表示,當制作不同寬度的互連原型並將其電阻與銅互連進行比較時,發現寬度為15nm或更小的石墨烯互連的電阻率低於銅互連的電阻率。石墨烯的接觸電阻率也比銅低四個數量級。將金屬離子嵌入石墨烯中可以改善互連的電性能,使其成為下一代互連的有前途的材料。

IMEC則認為石墨烯和金屬的混合結構,非常有希望成為1nm的候選者。此外,IMEC也在考慮釕 (Ru)作為銅互連的替代品。

04

改變器件架構

如上文提到,IBM對於1nm的努力除選擇釕互連外,還有一個就是VTFET架構。IBM認為,使用 VTFET,晶體管組件垂直堆疊在一起,而不是橫向堆疊,這是自計算機時代誕生以來設計芯片的標準。這極大地增加單個芯片上可以安裝的晶體管數量,就像摩天大樓城市的人口密度遠高於聯排別墅郊區的人口密度一樣。IBM的研究表明,VTFET 設計的規模可以遠遠超出 IBM Research 於 2021 年首次推出的最先進的 2 納米節點納米片設計的性能。

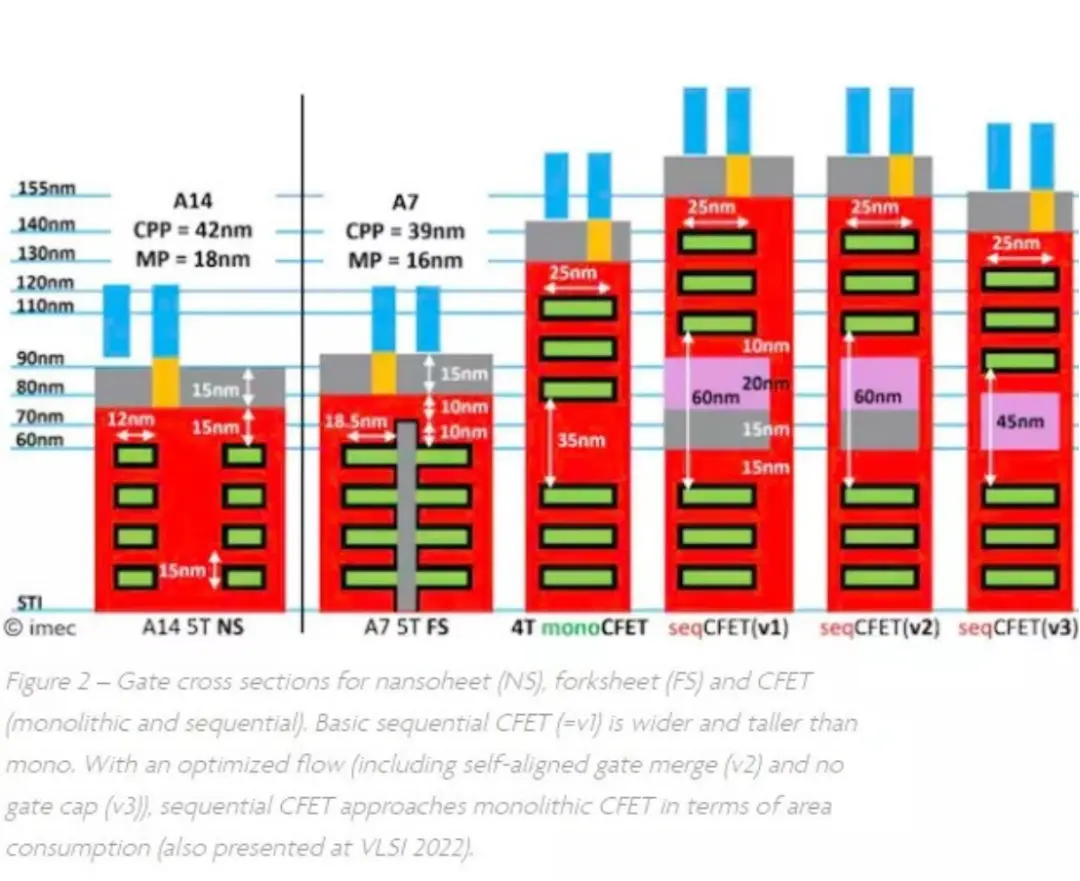

IMEC則認為能夠超越2nm的器件架構,是Forksheet架構。新的forksheet器件架構是 GAA 納米片器件的自然演變,允許軌道高度從 5T 擴展到 4.3T,同時仍然提供性能增益。或者,通過叉板設計,可用空間可用於增加板寬度,從而進一步增強驅動電流。

圖側四個結構,均為CFET的變種 來源:imec

英特爾則是認為可以使用一種GAA FET的最新形態——堆疊式CFET場效應管架構。這種架構的集成密度進一步提升,將n型和p型MOS元件堆疊在一起,可以堆疊8個納米片,比RibbonFET多一倍。目前,英特爾正在研究兩種類型的CFET:單片式(monolithic)和順序式(sequential)。不過,英特爾的CFET架構並不是獨立提出的,而是與IMEC機構長期合作的結果。

05

總結

在科技的世界裡,1nm無疑是一個極具吸引力的存在。然而,正如我們在文章中所提到的,1nm技術雖然具有巨大的潛力,但也帶來諸多挑戰。

對於許多公司和研究機構來說,1nm可能代表著技術上的“聖杯”。它不僅僅是一個物理極限,更是一個巨大的商業機會。例如,1nm晶體管會帶來更快的處理器,更小的內存單元,更高效的能源儲存等等。

通往1nm的道路可以謂是復雜又波折。產業界來看,這些學術的突破性進展並不一定能很快用於商業化的芯片生產。畢竟3nm芯片的良率似乎都還是一個問題。從3nm到1nm,摩爾定律如何延續,我們期待著更多的深入探索,以克服1nm技術所面臨的巨大挑戰。