在過去的幾十年裡,技術進步的一個途徑幾乎都是基於半導體實現的。半導體是其電導率可以變化多個數量級的材料,這使得可以選擇性地阻止和允許電子流動。這種特性使得制造各種電子設備成為可能,尤其是數字計算機。

隨著過去幾十年半導體技術的進步,電子計算的成本和規模穩步下降,使個人電腦、互聯網和移動電話成為可能。如今,能夠執行大量矩陣乘法的強大 GPU形式的半導體是推進人工智能技術的基石。越來越多的計算可用於進行大量搜索和學習,推動遊戲人工智能、計算機視覺和大型語言模型 (LLM)等領域的進步。

隨著摩爾定律的發展,晶體管(一種電子開關,集成電路的基本構建模塊)變得越來越小、越來越便宜。1954 年,第一臺晶體管收音機TR-1有 4 個晶體管,每個晶體管售價 2.50 美元(按 2024 年美元匯率計算為 29.03 美元)。如今,擁有 99 億個晶體管的AMD Ryzen 處理器售價為 650 美元,即每個晶體管約 0.000000066 美元。

換句話說,自 20 世紀 50 年代以來,晶體管的成本已下降約 3 億倍。

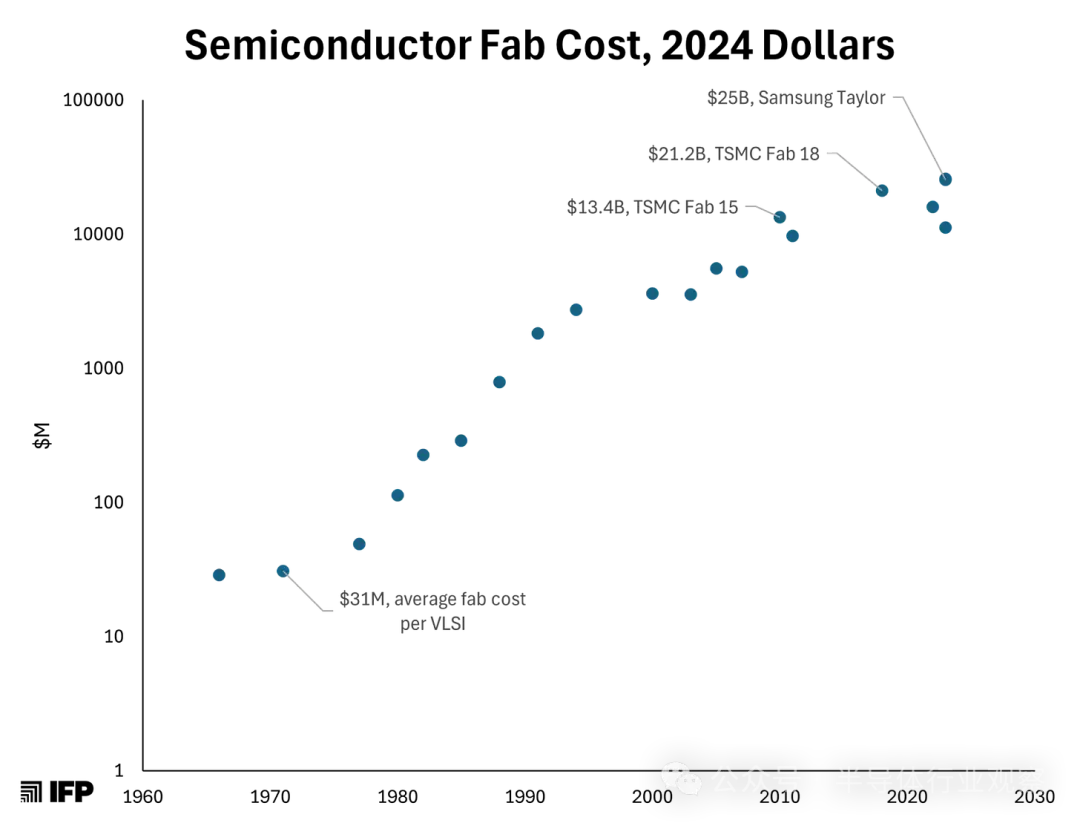

每個半導體元件都發生同樣的縮小和廉價化。但與此同時,制造它們的設施變得越來越昂貴。在 60 年代末和 70 年代初,半導體制造設施 (或“fab”) 的成本約為 400 萬美元(按 2024 年美元匯率計算約為 3100 萬美元)。如今,一座現代化晶圓廠的成本可能達到 100億至 200 億美元甚至更多。英特爾正在亞利桑那州建造兩座工廠,預計每座耗資 150 億美元,三星位於德克薩斯州泰勒的工廠預計耗資250 億美元。

這些巨大的成本最終是由於穩步降低半導體成本的同一因素造成的:摩爾定律,即集成電路上的元件數量每兩年就會增加一倍。(摩爾第二定律,也稱為洛克定律,規定半導體工廠的成本每四年就會翻一番。)半導體元件越小,創造制造條件就越困難。

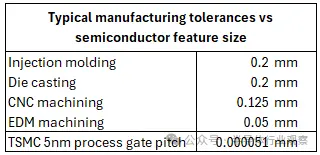

現代微芯片的寬度約為 50 納米,約為人類頭發寬度的 1/2000。材料被放置在幾個原子薄的層中。制造這麼小的物體需要超精密的制造設備,以及能夠屏蔽盡可能多的幹擾源的生產環境;每個流氓灰塵斑點或電壓的微小波動。而且這些條件必須在每年生產數億個微芯片的大規模生產設施中維持,而不是在實驗實驗室的稀薄條件下維持。超精密和大批量生產的結合造就世界上一些最復雜、最昂貴的工廠。

半導體制造工藝

要解為什麼現代晶圓廠如此昂貴,我們首先需要解制造半導體的工藝。

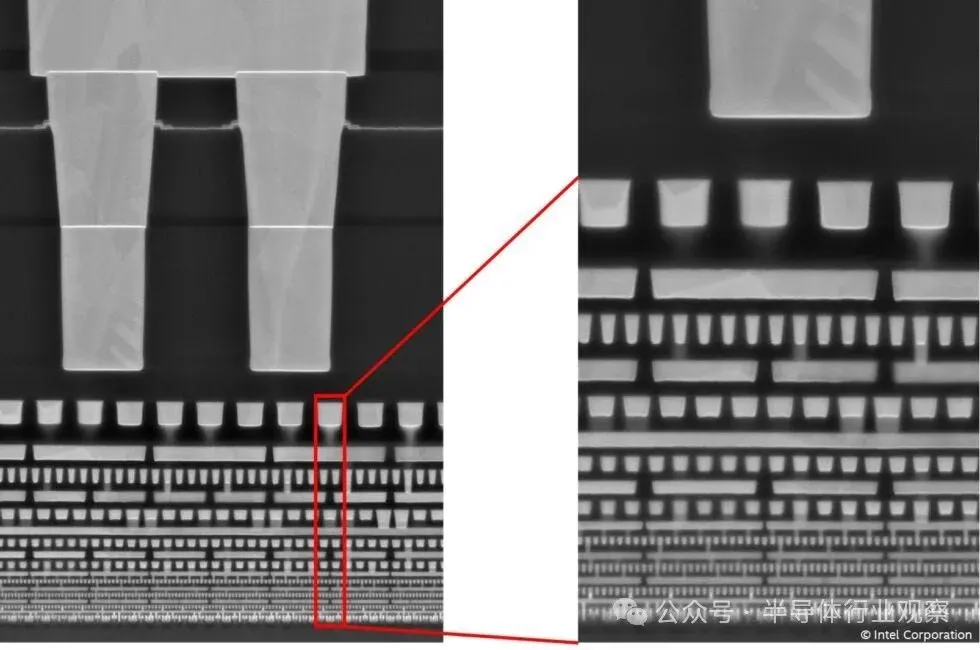

如果我們將計算機芯片從中間切開,並非常非常仔細地觀察,我們會發現它是由一系列層組成的。這是采用英特爾當前制造工藝制造的芯片的橫截面:

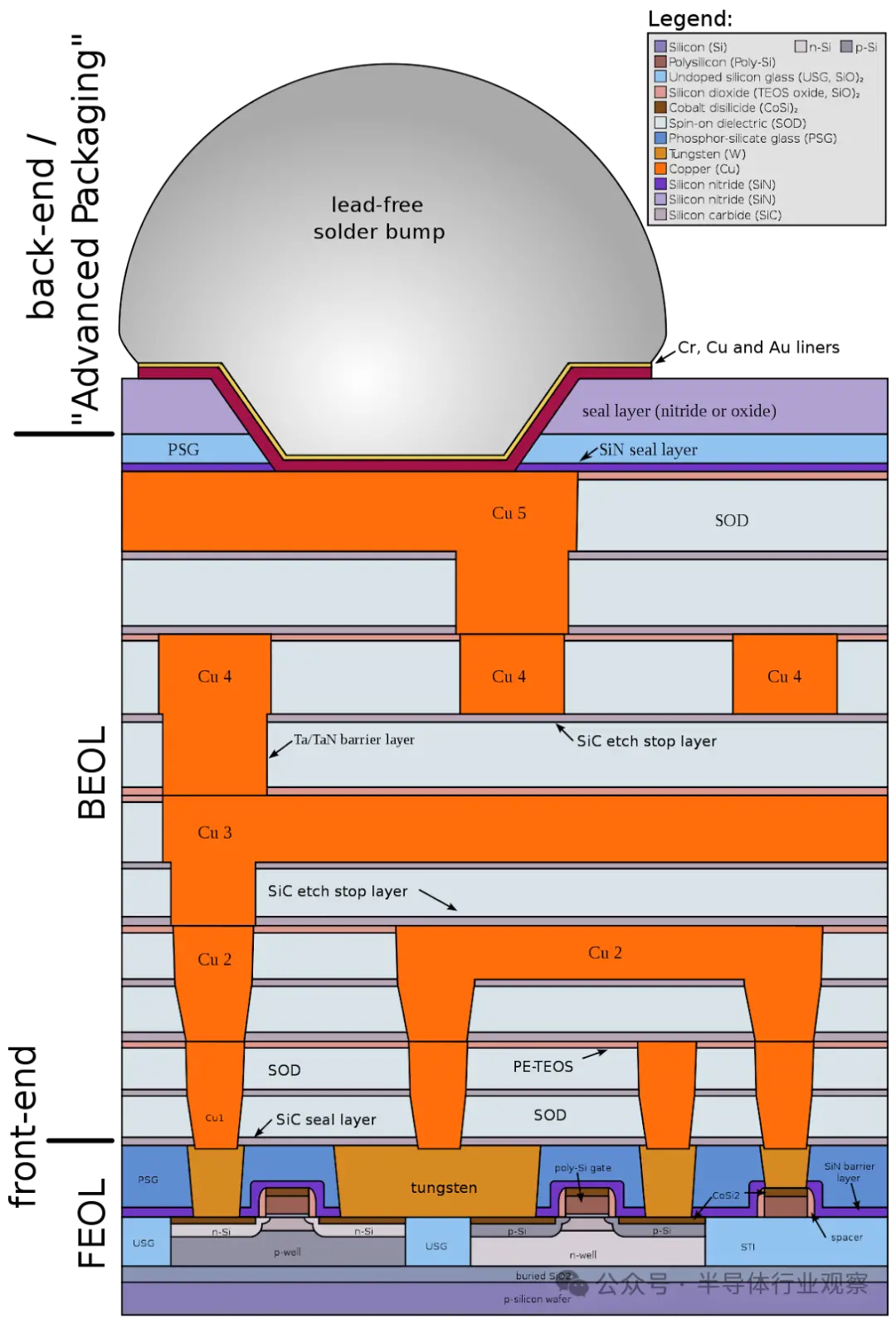

這是通用集成電路的橫截面圖,顯示不同的層:

在芯片底部,上圖中標記為 FEOL(front end of line)的區域是半導體元件本身:晶體管、電容器、電阻器、二極管以及用矽制成的用於制造微芯片的所有其他部件。這些單獨的組件將使用微觀金屬線連接在一起,區域中的層標記為BEOL(back end of line)。由於現代電子芯片中的元件數量巨大,因此佈線必須在單獨的層上佈線,這些層由稱為電介質的電絕緣體分隔開。例如,英特爾當前的工藝由15 層金屬佈線組成。該佈線通過層中稱為“通孔”的孔連接在一起並連接到半導體組件。

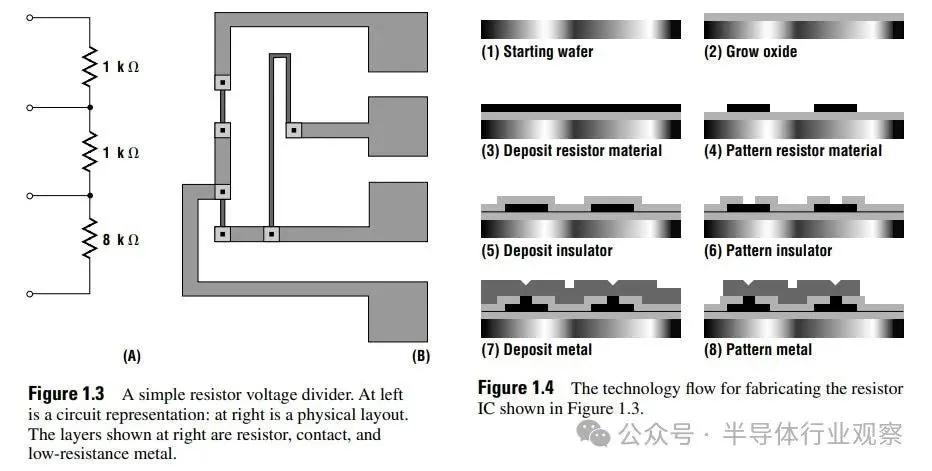

芯片是通過一次一層地構建這種復雜結構來制造的。從極純矽晶片開始,添加材料層,去除部分層,添加更多材料(或修改現有材料),依此類推,直到整個結構完成。這種制造方法稱為平面工藝,由 Jean Hoerni 於 1959 年在 Fairchild Semiconductor 發明,它使集成電路和現代計算機技術成為可能。

構建微芯片結構的過程可以分為四個重復應用的基本操作:增層(layering)、圖案化(patterning)、摻雜(doping)和退火(heat-treating)。

1.增層

增層用於在晶圓表面添加一層極薄的材料(小至納米或更小,僅為人類頭發厚度的 1/100,000)。這些層可能是絕緣體(例如用於分隔組件的二氧化矽層)、導體(例如用於連接組件的銅佈線層)或半導體(例如構成半導體組件一部分的外延矽薄膜)。

根據工藝步驟和所使用的材料,可能會應用不同的分層技術。

隨著特征的縮小,沉積方法也隨著時間的推移而發展。目前常見的增層方法包括熱氧化(將晶圓暴露在熔爐中的氧氣中,從而在晶圓表面形成一層薄薄的二氧化矽)、化學氣相沉積 (CVD)(將氣態化學物質聚集在一起,將其反應物沉積在表面上)晶圓)和濺射(用等離子體離子轟擊固體材料,導致原子脫離並沉積在晶圓表面)。現代半導體元件的小尺寸要求這些分層方法具有極高的精度。例如,現代原子層沉積方法能夠一次創建單層原子。

2.圖案化

圖案化是在晶圓上刻出特定圖案的過程,根據需要選擇性地去除材料以制造電子元件。在現代半導體上,這是通過光刻來完成的。

首先在晶圓上塗上一層薄薄的光敏材料,稱為光刻膠。特定波長的亮光穿過稱為掩模的玻璃或石英板,掩模上刻有要在晶圓上創建的圖案。掩模包含單個芯片所需的圖案,但晶圓將包含數百個單獨的芯片。為曝光每一個,使用步進機或掃描儀將掩模在晶圓表面上來回移動。未被掩模阻擋的光線穿過並在光刻膠中引發化學反應;

使用正性光刻膠,暴露在光線下的區域會變弱並變得可溶;對於負性光刻膠,曝光區域會硬化,而光刻膠的其餘部分仍然可溶。無論哪種情況,晶圓在曝光後都會被清洗,在需要塗覆的圖案中留下一層硬化的光刻膠。

從這裡開始,晶圓將被蝕刻:腐蝕性化學物質將被施加到晶圓上,腐蝕掉被去除的光刻膠暴露的材料,並將圖案刻在晶圓本身上。蝕刻可以是“濕式”(通過將晶圓暴露於氫氟酸等液體化學品中)或“幹式”(通過將晶圓暴露於已被激發成等離子體的氟等氣體中)。

蝕刻後,去除剩餘的光刻膠。

3.摻雜

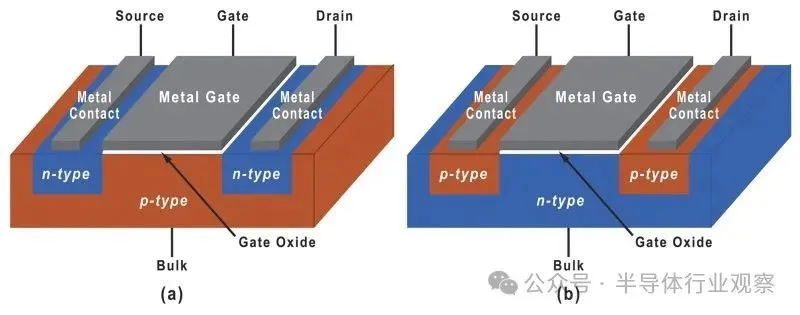

摻雜是將極少量的雜質引入半導體材料以改變其電導率的過程。通過在矽中摻雜少量的V 族元素(例如磷或砷),可以產生具有過量自由電子的 n 型半導體。通過摻雜少量的III 族元素(例如硼),可以產生具有過量電子空穴的 p 型半導體。通過適當排列 p 型和 n 型矽,可以制造晶體管等組件。

MOSFET 中的 p 型和 n 型半導體

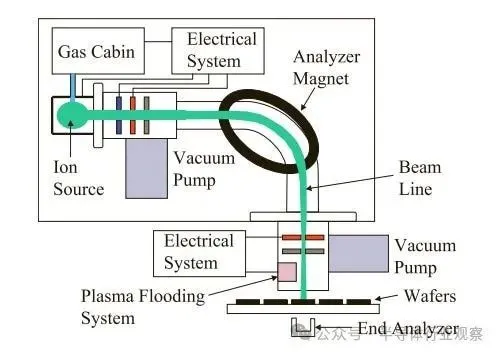

早期,在半導體制造中摻入雜質的主要方法是擴散:通過在氣體存在下加熱晶圓,氣體原子會擴散到晶圓表面。但如今,摻雜主要通過離子註入來完成:一束離子(具有過量或缺乏電子的原子,賦予它們電荷)被發射到晶圓上,將原子沉積在表面下方。

離子註入裝置

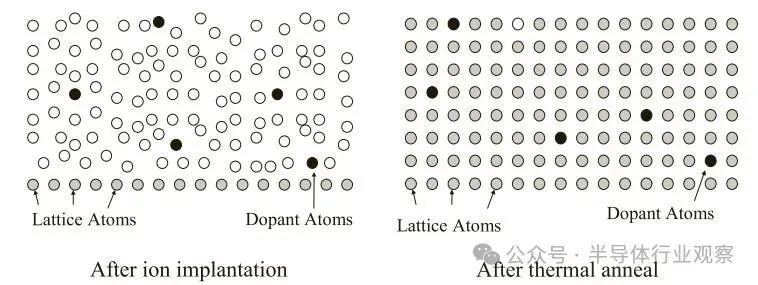

4.退火

半導體制造中的最後一個主要操作是退火。該過程中有許多步驟,其中加熱或冷卻晶圓以獲得特定結果。例如,離子註入會導致矽晶體結構受損。這種損壞可以通過快速熱退火來修復;熱燈在幾秒鐘內將晶圓加熱到 1,000 度以上,然後晶圓緩慢冷卻,修復晶體結構。在光刻過程中還使用加熱來“烘烤”並硬化液體光刻膠。

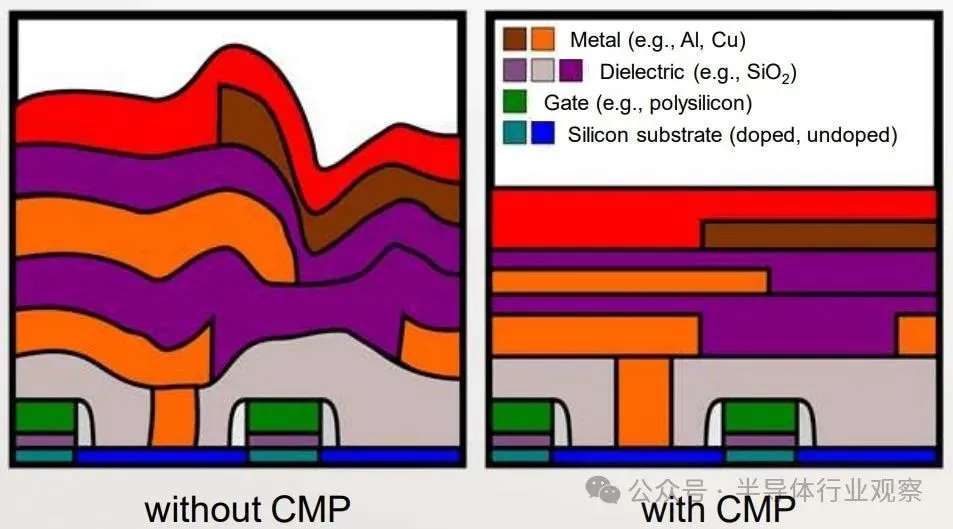

除這四種基本工藝之外,半導體制造還涉及許多其他支撐工藝。一個關鍵的支持過程是拋光:因為微芯片是由數十個單獨的層構成的,隨著更多層的添加,層厚度的變化將隨著時間的推移而傳播,如果不加以解決,就會導致問題。

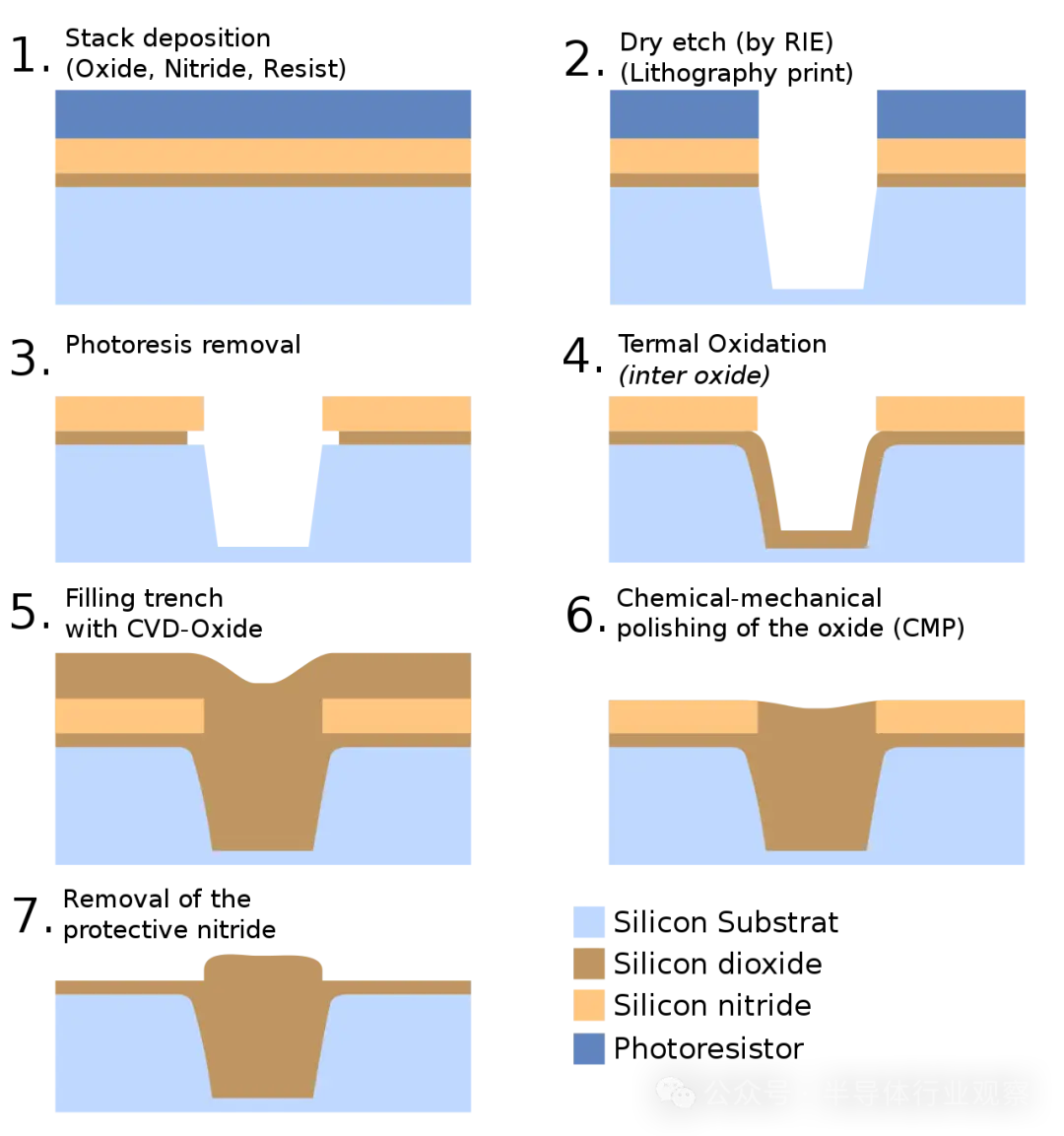

為解決這個問題,在制造過程中經常使用化學機械拋光(CMP)對晶圓進行拋光,以使晶圓表面光滑。CMP 還用於填充蝕刻產生的孔,方法是在整個晶圓上塗上一層材料,然後拋光掉孔上方的材料。

使用和不使用 CMP 的晶圓表面

CMP 用於用二氧化矽填充溝槽的過程中

另一個關鍵的支持過程是清洗。

由於最微小的雜散顆粒都會導致微芯片發生故障,因此必須不斷用溶劑和極純水清潔晶圓。在現代晶圓廠中,晶圓在生產過程中可能會被清洗200 次或更多次。為確保工藝正常運行,晶圓廠廣泛使用計量技術——在工藝的各個點測量晶圓,以確定是否存在任何制造錯誤或缺陷。

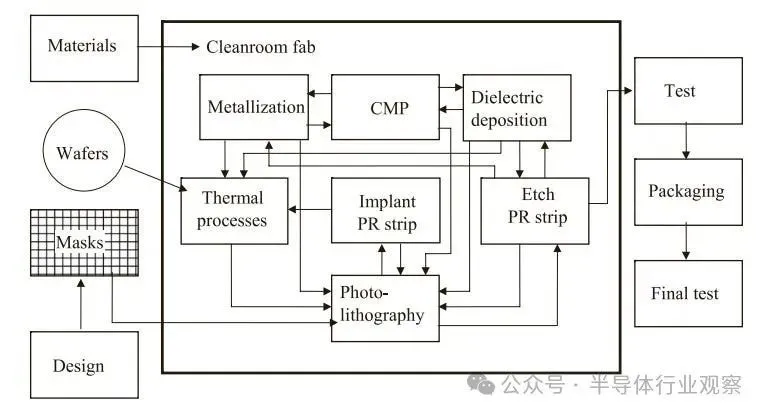

半導體工廠的工藝流程圖

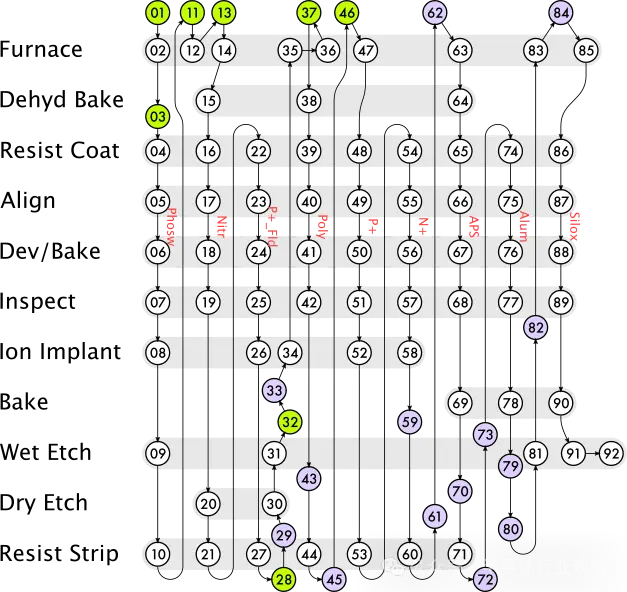

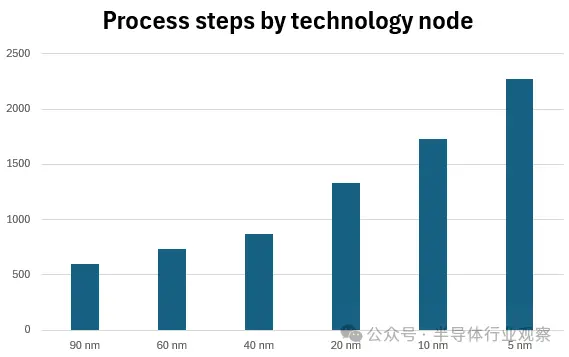

通過一遍又一遍地應用這四個基本過程,以及各種支撐過程,微芯片的結構慢慢地建立起來。隨著越來越多的晶體管被塞進集成電路中,這種結構(以及創建它的過程)變得越來越復雜。早期的集成電路隻需五到十個不同的掩模和數十個工藝步驟即可制成,但現代的尖端微芯片可能需要 80 個或更多掩模和數千個單獨的工藝步驟。

大約 20 世紀 80 年代的簡單九掩膜 CMOS 芯片的工藝流程。如今,尖端芯片需要 80 個左右的掩模,並且工藝流程更加復雜。

一旦晶圓完成所有這些步驟並且電路結構完成,就可以進行組裝和封裝。在這裡,晶圓被切割成單獨的芯片,每個芯片都連接到電線(以及任何其他芯片,就像先進的封裝一樣),並封裝在保護塗層中。封裝可以在半導體工廠完成,也可以完全在另一個工廠完成。

半導體制造的難度和費用

就其本身而言,大量的工藝步驟並不需要價值 200 億美元的制造設施。畢竟,許多復雜的制成品需要同樣多或更多的步驟來生產。例如,一塊20 世紀早期的手表由 150 個零件組成,需要 3700 多道工序才能生產。

但當這些工藝步驟被用來制造尺寸為十億分之一米的組件時,制造的復雜性就會大大增加。對於大多數制造過程,即使是那些使用精密方法生產可互換零件的制造過程,也存在相當程度的公差。如果零件太長或太短一毫米,它仍然適合。如果金屬的雜質含量稍微高一點,該金屬仍然可以使用。如果進程運行得稍微太快或太慢,輸出仍然可用。

在半導體制造中,允許的公差幾乎被削減到零。制造幾納米尺寸的晶體管需要比傳統制造精確數十萬倍的工藝。最微小的流氓粒子(rogue particle)就能使連接短路並毀壞整個芯片。一些原子位於錯誤的位置可能會導致工藝步驟失敗。難以察覺的少量雜質可能會對材料造成不可挽回的損壞。

半導體制造的歷史就是一部針對這些微小影響及其災難性影響的無休止戰爭的編年史。即使要讓半導體器件正常工作,也需要極其密切地關註化學濃度和不良雜質。20 世紀 40 年代,貝爾實驗室研究半導體時,神秘的組件故障最終被追溯到研究人員觸摸銅門把手;從門遷移到工人手中的極少量銅原子就足以毀掉他們的工作材料。早期的半導體制造商發現,他們的工藝受到月相、工人最近是否上過廁所,甚至女員工的月經周期等因素的影響。

隨著半導體特征變得越來越小,問題隻會變得更加困難。隨著晶體管的縮小,英特爾發現,即使是最無害的設備變化(例如使用稍長的管道或電纜)也可能導致新工廠的工藝中斷,並導致數月或數年的良率下降。為解決這個問題,英特爾制定一個名為“ Copy EXACTLY”的流程。新工廠將盡可能與現有工廠相同,甚至包括墻壁油漆的顏色和品牌。

因此,現代半導體工廠必須創造一個具有令人難以置信的精度和可預測性的世界。每一個可能擾亂制造過程的影響,無論多麼小,都必須被篩選出來,任何細微的偏差都必須被追查和消除。這種控制必須在大規模生產環境中維持,每年生產數十萬個晶圓和數百萬個單獨的芯片(每個芯片都有數十億個晶體管)。

晶圓廠的結構

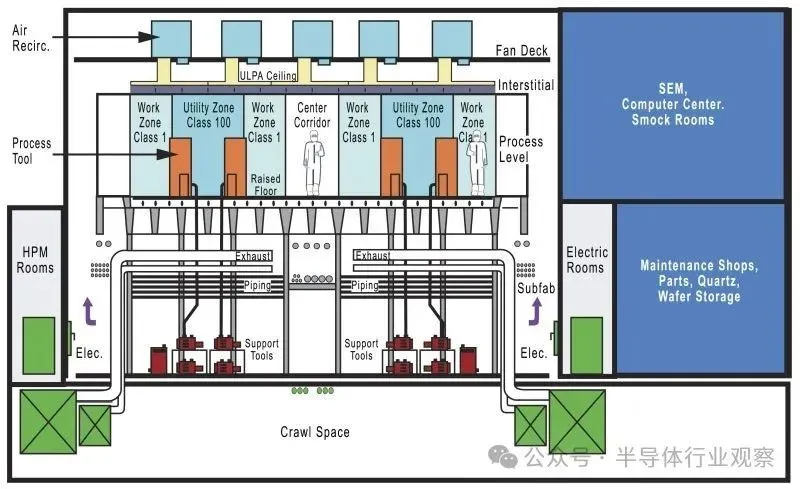

為創建這種環境,現代半導體工廠通常由四層組成。

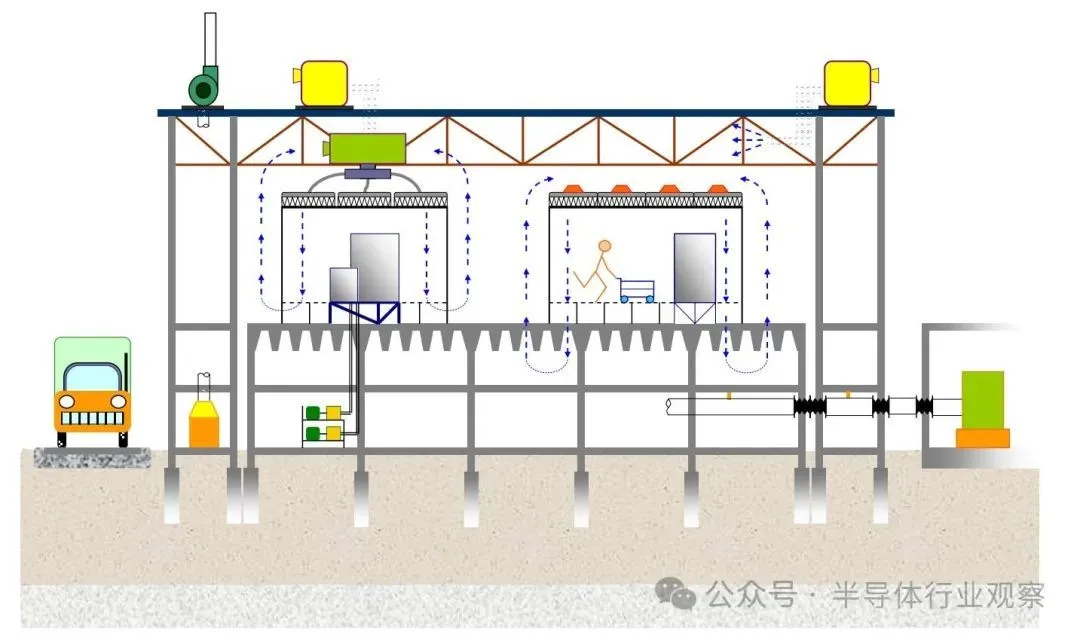

晶圓廠的核心是潔凈室層;實際進行制造過程的工廠車間潔凈室下方是次級晶圓廠,一層或多層(通常為兩層),其中包含支持潔凈室操作所需的管道、管道、佈線和設備。潔凈室層上方是一個間隙空間,配有風扇和過濾器,用於將空氣再循環到下面的潔凈室。

潔凈室層包含工藝工具:執行上述各種操作的各個設備。工具范圍從光刻機(如ASML的EUV機),到化學氣相沉積機,到離子註入機,到用於清潔和蝕刻的“濕工作臺”(wet benches)等等。這些機器由ASML 、Lam Research 、Applied Materials和Tokyo Electron等少數專業制造商制造,而且價格極其昂貴。主要加工機器的成本可能為 500萬至 1000 萬美元,有些可能高達 1 億美元。ASML 的尖端光刻機耗資近 4 億美元。

這些工具可能執行一個特定的工藝步驟(例如用於晶圓加熱的熔爐)或集成多個單獨的工藝步驟。例如,應用材料公司制造機器其中包含多個layering和表面處理步驟。為生產大量晶圓(現代微處理器或“邏輯”晶圓廠可能每月生產 40000 至 50,000 個晶圓;生產存儲器的晶圓廠可能每月生產 120,000 個晶圓),需要大量工具——1,000 個或更多。

工藝工具將按類型聚集在一起;這使得這些工具可以共享化學品和天然氣管道等的需求(如果某種化學品的所有需求都集中在一個地方,則運行管道會更容易),並且可以隔離某些污染物。由於銅雜質會對半導體行為產生災難性影響,因此使用銅的工藝部分(例如沉積微觀銅佈線的工具)可能與工廠的其他部分隔離。HVAC 系統同樣會在不同的過程區域之間進行隔離。為最大限度地減少柱子或承重墻等物體的幹擾,工廠的屋頂通常由大型、長跨度的桁架支撐,從而使潔凈室空間盡可能開放。

美光晶圓廠潔凈室地板上的工藝工具

正在建設中的英特爾晶圓廠,展示橫跨潔凈室地板的大型桁架

潔凈室的設計旨在最大限度地減少污染。

半導體工廠通常采用10 級或 100 級潔凈室建造,這意味著每立方英尺空氣中最多可以有 10 或 100 個 0.5 微米或更大的顆粒。相比之下,普通房屋每立方英尺空氣中含有約 500,000 個顆粒,而外科手術室則含有約100,000 個顆粒。)為實現這一目標,大型空氣處理裝置迫使空氣通過潔凈室天花板中的 HEPA 或 ULPA 過濾器。空氣通過地板被拉入次級晶圓廠,然後通過天花板一遍又一遍地再循環。

晶圓廠的橫截面

為防止潔凈室外部的顆粒進入,潔凈室相對於外部保持正壓。將空氣保持在所需的清潔度水平意味著每小時要更換數百次空氣,而典型的辦公樓每小時要更換 5-10 次空氣。這種氣流量,加上半導體潔凈室的大小(大型晶圓廠可能為500,000-1000000平方英尺或更多),意味著晶圓廠的 HVAC 系統非常龐大。

除這些大型暖通空調系統外,潔凈室中使用的材料和工藝工具也需要經過專門設計,以防止排放顆粒。為最大限度地減少潔凈室內人員的污染,工作人員在進入之前在特殊的更衣區穿上兔子服,並經過特殊的清潔程序。

隨著半導體功能的縮小,潔凈室的要求變得更加嚴格。

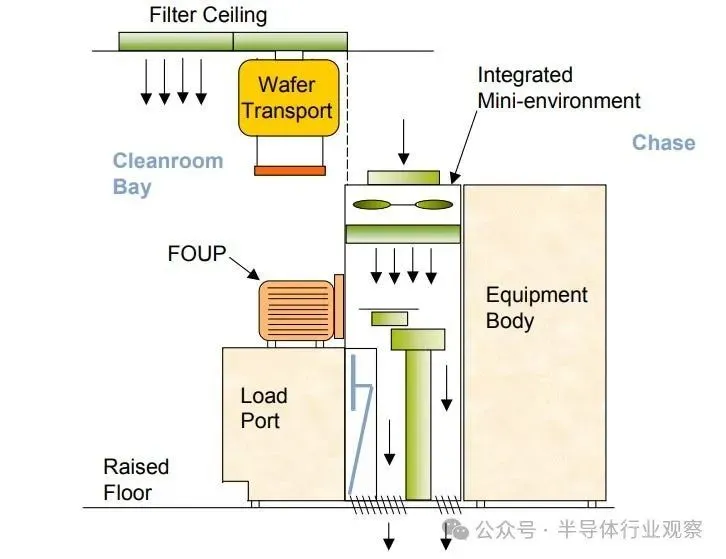

在 20 世紀 80 年代,晶圓廠潔凈室是按照 1000 級標準建造的,但到 1990 年代,一些制造商正在建造極其潔凈的1 級潔凈室(每立方英尺空氣中隻有一個 0.5 微米的顆粒)。由於達到這種清潔度水平的成本很高,因此制造商采取將晶圓與潔凈室其他部分隔離的策略。

晶圓在稱為 FOUP(front opening unified pods:前部開放式統一盒)的密封盒中的工藝工具之間傳輸,並且工藝工具本身是封閉和密封的。

例如,這傢臺積電晶圓廠是用 100 級潔凈室建造的,但晶圓本身是在 0.1 級“微型環境”內處理的。通過采用微環境策略,晶圓廠能夠去除空氣中更多的雜質,而無需凈化潔凈室中數百萬立方英尺的空氣。

顯示帶有工具微型環境的 FOUP 的繪圖。

FOUP 使用自動材料處理系統在工藝工具之間移動。在大多數現代晶圓廠中,這由安裝在天花板上的軌道系統組成(盡管一些晶圓廠,尤其是較舊的晶圓廠,可能會使用基於地板的自動引導車)。

專門設計的車輛在一個處理工具處拾取 FOUP,然後將其送到下一個處理工具處。大量的制造步驟意味著晶圓可能需要數月的時間才能完成整個過程。再加上晶圓廠每月生產的大量晶圓,意味著在任何給定時間,生產過程中的各個點都有數以萬計的晶圓,在工具之間來回移動或儲存起來等待輪換。

在生產過程中,晶圓將在不同的生產工具之間來回行駛數英裡。因此,運輸系統必須是廣泛的,擁有數英裡的軌道和數百或數千輛運輸車輛。它們必須經過精心設計,以避免出現瓶頸,讓“流量”順暢流動。

FOUP AMHS

當 FOUP 到達處理工具時,可以將其連接到特殊的裝載點,並且可以在機器的受控環境中自動處理晶圓。處理後,晶圓可以裝載到另一個 FOUP 中並移至下一個工具。由於工藝工具可能無法立即可用,因此 FOUP 會一直儲存起來,直到有空位並可以移動它們為止。儲存中的 FOUP 偶爾會用氮氣沖洗,以確保污染物不會到達內部的晶圓。

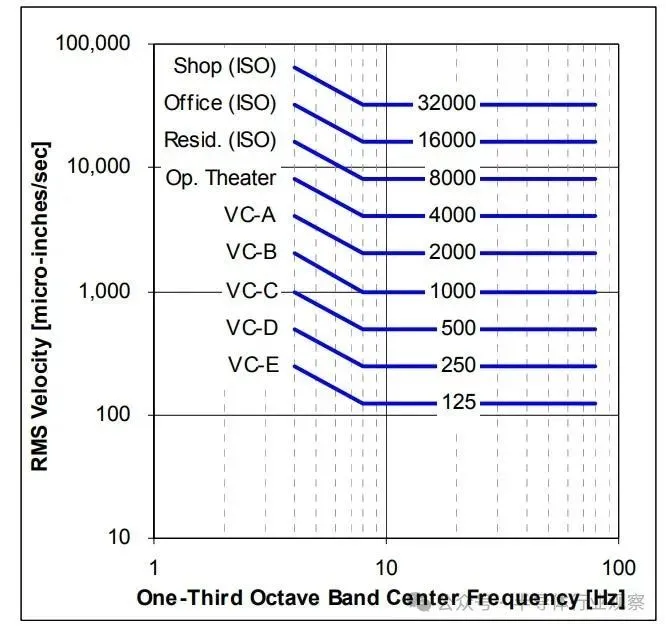

但流氓顆粒(rogue particles)並不是唯一會破壞制造過程的因素,工廠的每個部分,從潔凈室到基礎,都必須設計成最大限度地減少外部幹擾。所需的極高精度意味著工藝工具對振動極其敏感(即使是巨大的噪音也會對制造過程產生負面影響),而晶圓廠的設計旨在最大限度地減少振動。

晶圓廠通常建在遠離機場、鐵路線、繁忙的高速公路和任何其他重要外部振動源的地方,而且晶圓廠配套設施本身也必須設計成消除振動。(在一個案例中,不可接受的潔凈室地板振動是由距晶圓廠大樓 400 英尺的排氣口引起的。)晶圓廠內大量可能產生振動的機械和設備(例如電機、泵、HVAC 系統,甚至管道中的流體流動)。工廠必須將振動限制在感知閾值以下幾個數量級,同時吸收傳統建築 100 倍的機械能和 50 倍的氣流。

不同建築類型的振動要求。現代半導體工廠中最敏感的區域是按照 VC-D 或 E 要求甚至更高的要求建造的

為最大限度地減少振動,潔凈室的地板通常建造為兩到四英尺厚的深混凝土華夫板(deep concrete waffle slab ),由緊密間隔的柱子支撐,以使其盡可能堅硬。樓板上方是凸起的金屬地板,允許管道和電纜在其下方佈線,並允許將加工工具放置在單獨的支撐基座上,以防止工人的腳步引起振動。

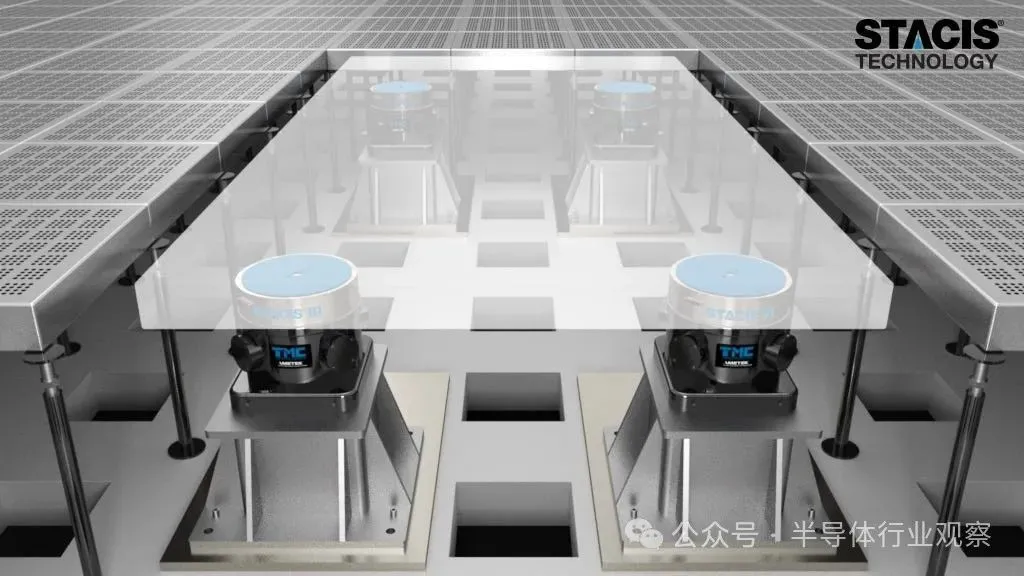

一些極其敏感的設備,例如光刻工具,可能需要更嚴格的措施,例如可以感知並消除任何異常振動的主動減振器。在某些情況下,晶圓廠可能會建造一個結構隔離斷層,以保持潔凈室地板與建築物的其他部分以及它可能引起的任何振動物理隔離。

具有主動減振功能的半導體工具基座,與高架潔凈室地板分開

半導體工廠結構隔離中斷的概念

理想情況下,防止振動還意味著將您的工廠放置在地震不活躍的區域。當不可能時(例如在臺灣或日本),可能會采取其他措施,例如添加地震阻尼器或使用特殊的地基將建築物與周圍的土壤隔離。

除顆粒和振動之外,晶圓廠還需要消除許多其他幹擾源。為防止光線意外曝光光刻膠,光刻區域通常使用不會曝光化學物質的特殊黃光。地板等必須使用防靜電材料,以防止靜電積聚。工具對電磁幹擾很敏感(甚至附近電源線的磁場也可能導致設備中斷),因此必須屏蔽工具並盡量減少 EMF 源。晶圓廠擁有備用發電機和不間斷電源,以防停電,設備的設計必須能夠應對公用電源的電壓變化。(在提出這一要求的設計標準之前,公用電壓變化導致半導體制造問題顯然很常見。)潔凈室中的溫度和濕度必須保持在一個狹窄的范圍內,這給 HVAC 系統帶來進一步的負擔。

出於安全目的,晶圓廠還可以設計為射頻 (RF) 屏蔽。

在潔凈室精心控制的條件之下是次級晶圓廠:支持潔凈室操作所需的一層或多層設備。例如,EUV 光刻機是一種卡車大小的復雜設備,但潔凈室工具隻是所需總設備的一部分。潔凈室下方是驅動 EUV 系統的巨大 CO2 激光器,以及在工藝室內產生真空所需的泵。許多其他工藝工具,例如離子註入機和濺射機,也需要真空,大型晶圓廠的子晶圓廠可能有數千個真空泵。

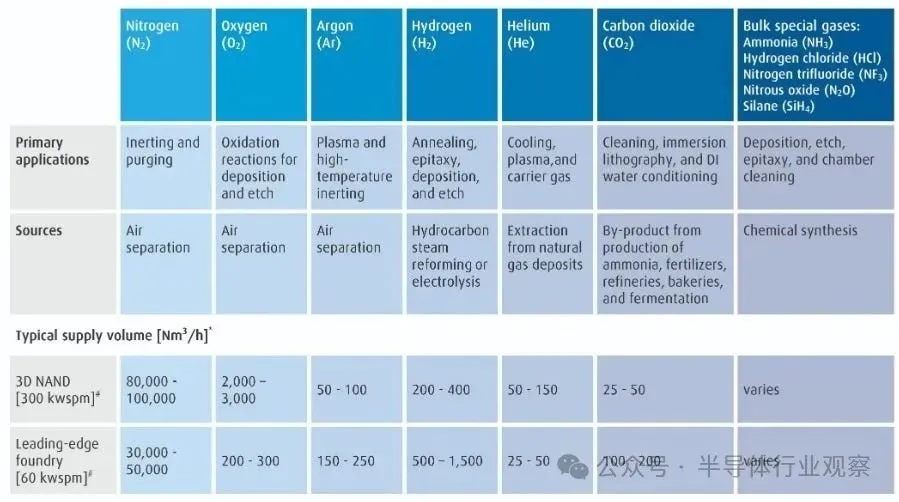

通過Crystal5D Technologies渲染下方子晶圓廠中帶有支持設備的工藝工具

次級晶圓廠也是工藝工具所需的許多化學品的存儲和輸送場所(盡管一些化學品,特別是劇毒化學品,將存儲在工藝工具內以最大程度地減少泄漏風險,而其他化學品將存儲在工藝工具外)很棒的建築)。半導體工廠使用多種化學品,包括氮氣(用於凈化和清潔 FOUPS 和工藝工具)、氧氣(用於氧化爐和減排設備)、氬氣(用於等離子體反應)、氫氣(用於 EUV 機器)清潔)等。使用的化學品和氣體的數量以及產生的廢氣量需要大量的管道,有些管道的直徑可達十英尺。而且這些化學物質必須極其純凈,在某些情況下純度可達 99.9999999%。

半導體氣體

子晶圓廠中的管道

工廠中使用的許多化學品,例如用於摻雜的磷化氫和砷化氫,都具有劇毒。其他化學物質,例如某些 CVD 工藝中使用的矽烷,是自燃的(這意味著它們會在空氣中自燃。)一種化學品,用於清潔 CVD 室的三氟化氯,毒性很大,很容易自燃(它能夠使濕氣凝結)著火的沙子),一些化學傢拒絕使用它。由於這些化學品具有危險性,因此需要特殊的處理和泄漏檢測系統、備用電源系統以及專門設計的消防系統。

次級晶圓廠還包含用於處理工藝工具產生的各種副產品的排氣系統。為防止副產品(特別是氨)相互反應,必須使用多個單獨的排氣系統。許多過程需要減排設備(將燒掉任何有害副產品)或洗滌器來去除有害物質。該設備可能安裝在加工工具本身上,或者是集中排氣系統的一部分。

除化學品處理和排氣設備外,副晶圓廠還包含配電箱、變壓器、風扇、空氣處理器、冷卻器、射頻發生器、熱交換器以及保持晶圓廠工具運行所需的所有其他設備。子晶圓廠通常分為“潔凈”子晶圓廠(來自潔凈室的空氣再循環)和其下的單獨“臟”或公用子晶圓廠。

雖然次級晶圓廠的控制水平可以有所放松(工人不需要在其中穿兔子服),但仍必須盡量減少變化和潛在的幹擾。即使電壓、壓力或振動的微小變化,或者管道發出的最小顆粒,也會對制造過程產生負面影響。

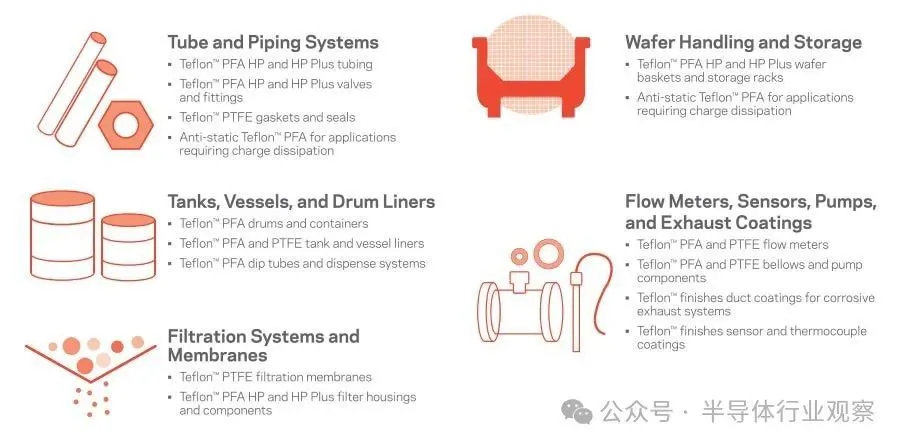

實現這一目標意味著次級晶圓廠設備的制造必須比傳統制造更加嚴格的要求和更嚴格的公差。管道、泵和其他物料搬運設備等均采用不銹鋼和聚四氟乙烯塗層。管道內部必須進行電解拋光,以防止顆粒排放或為污染物積累提供場所,並且管道必須使用特殊的軌道焊接方法連接,以防止泄漏或污染。

通常,次級晶圓廠設備和材料本身必須使用專門的制造程序在潔凈室中制造,並用塑料袋雙層包裝運輸到工作現場,以防止運輸過程中受到污染。所有化學品和氣體管道和處理系統的設計必須能夠提供平穩、不間斷的物料流;即使壓力的微小變化也會對生產過程產生“災難性”影響。

晶圓廠中使用特氟龍塗層

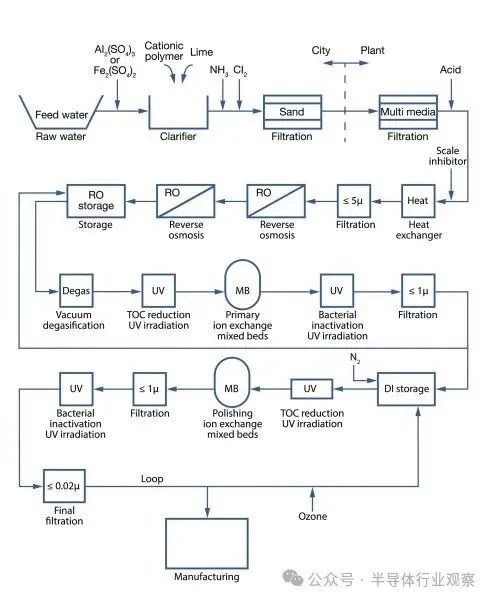

在次級晶圓廠之外,還需要許多其他設施來支持潔凈室操作。將重型加工工具移入潔凈室需要能夠舉升數萬磅的工業電梯。晶圓廠使用大量的氮氣和氧氣(大型邏輯晶圓廠每小時可能使用 50,000 立方米氮氣),因此晶圓廠通常會在現場配備空氣分離設備,產生氮氣、氧氣和氬氣等氣體。同樣,晶圓廠將使用大量超純水進行晶圓清洗和 CMP,並使用常規水用於冷卻器等工藝冷卻。一座大型工廠每天可以使用數百萬加侖的超純水,相當於一個擁有 50,000 人的城鎮的水量,而生產超純水需要擁有自己的專業工廠。

與晶圓廠的其他方面一樣,隨著功能的縮小,對超純水的要求也變得更加嚴格。其他晶圓廠支持設備包括鍋爐、冷卻器、應急發電機和廢水處理。

超純水生產工藝

所有這些設備和過程都消耗大量能源。一座大型晶圓廠可能需要 100 兆瓦的能源,或大型核反應堆容量的 10%。大部分能量由工藝工具、HVAC 系統和其他加熱/冷卻系統使用。對電力和水的需求非常嚴重,以至於當當地公用事業公司無法保證供應時,一些工廠被取消或搬遷。為確保工廠保持適當的條件,使用數萬個傳感器來監測顆粒水平、壓力和雜質水平等。

建設晶圓廠

大型晶圓廠將擁有數十萬平方英尺的潔凈室,並且該設施可能占地數百英畝。建造它需要數萬噸結構鋼和數十萬碼混凝土。英特爾宣稱其工廠使用的混凝土是哈利法塔的兩倍,金屬的使用量是埃菲爾鐵塔的五倍。

將這種材料以必要的精度水平安裝到位需要數千名經過專門培訓的建築工人。

英特爾在馬格德堡的新工廠預計在高峰期需要超過 9,300 名工人,而臺積電在亞利桑那州建造的新工廠則需要12,000 名工人。工人必須遵循專門設計的“清潔施工”協議,以保持材料清潔,最大限度地減少顆粒侵入,並確保潔凈室在完工後能夠成功運行。

在某些情況下,這意味著使用設備“吃掉”焊接煙霧,以及在現場切割的任何物體的邊緣塗上環氧樹脂漆以防止顆粒排放。為滿足所需的清潔度和精度水平,管道和機械設備可能會在現場預制,然後交付和安裝。為幫助明確要求,半導體行業協會SEMI發佈有關設施設計和設備生產各個方面的大量標準和設計指南。

一旦工廠竣工,潔凈室可以保持正壓(稱為“排污”),就可以安裝工藝工具。設備可能會分成許多單獨的部件到達,需要漫長而仔細的組裝過程——ASML 的一臺先進 EUV 機器“裝在 40 個貨運集裝箱中,分佈在 20 多輛卡車和三架貨機上。”

我們還必須小心處理工具:生產工具的敏感性意味著設備掉落或碰撞可能會導致延誤和數百萬美元的維修費用。一旦安裝工具,晶圓廠可能需要六個月到一年的時間才能達到可接受的工藝良率。

盡管晶圓廠規模龐大且復雜,但其建設速度卻驚人地快,平均大約需要兩到四年。這與其他大型商業建築項目並沒有什麼不同,而且比其他一些嚴格控制的過程設施(如核電站)要快得多。

然而,在美國,晶圓廠的建設速度比世界其他地方要慢。

美國晶圓廠建設時間從 1990 年代的平均 650 多天增加到 2010 年代的平均 900 天以上,而亞洲國傢的平均建設時間約為 600-700 天,部分原因是環境審查流程日益嚴格。美國晶圓廠的建造成本也比世界其他地區更高,估計貴出 30%(根據英特爾)到四倍(根據臺積電)。

晶圓廠成本明細

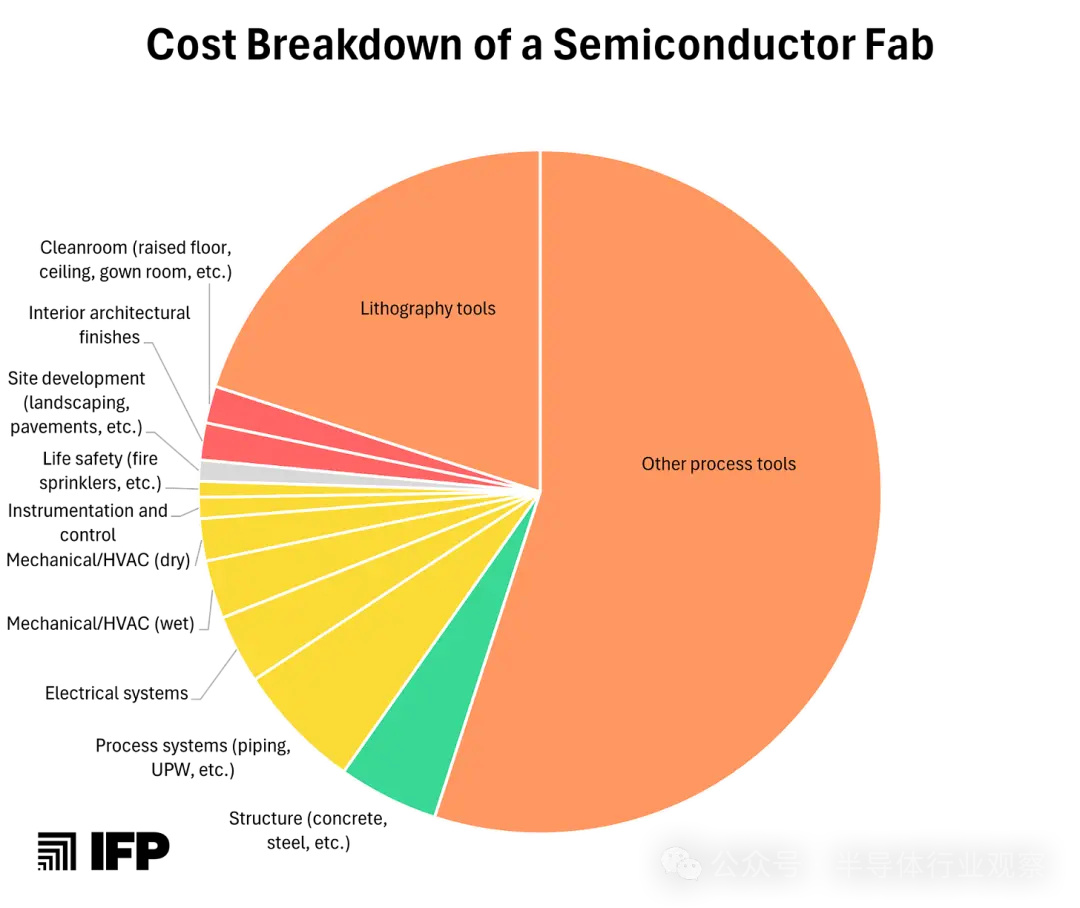

建設晶圓廠如此昂貴並不奇怪:它們龐大、復雜,並且具有極其嚴格的性能要求。但晶圓廠的存在是為為數千個工藝工具的運行提供必要的環境,而這些工具是迄今為止建造新晶圓廠最昂貴的部分。新晶圓廠大約 70-80% 的成本將用於其中的工藝工具。(這樣做的一個副作用是,升級現有晶圓廠以使用更先進的工藝節點所花費的成本隻是全新晶圓廠成本的一小部分。)

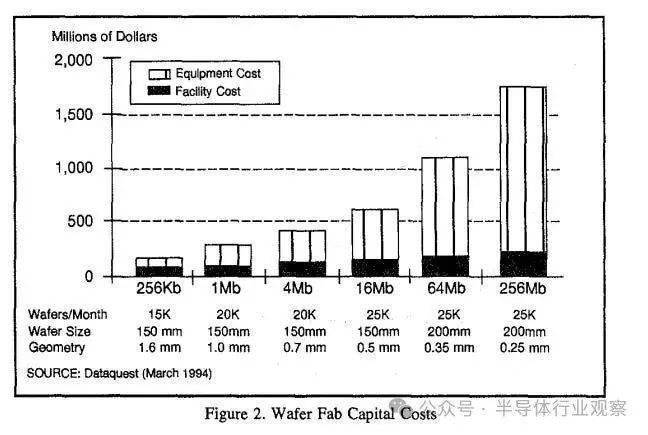

隨著時間的推移,設備在晶圓廠成本中所占的比例不斷上升。例如,20 世紀 80 年代中期的 DRAM 工廠,設施和設備成本大致均等,但到 90 年代末,設備占據成本的絕大部分。

DRAM 晶圓廠的建設成本與設備成本

對於建築成本,我們看到與單戶住宅的成本有些類似的細目,包括結構、建築飾面、現場工作和景觀美化、服務和機械系統等項目。主要區別在於,晶圓廠的機械、電氣和其他服務所占比例要高得多。超純水設施、多個排氣系統和巨大的 HVAC 需求等意味著服務費用占新工廠成本的近 2/3,而單個傢庭住宅的成本還不到 20%。

就設備成本而言,最大的支出通常是光刻機,其次是沉積、清潔和蝕刻設備。光刻機的成本通常估計為新晶圓廠成本的 20%,這意味著光刻工具的成本可能與整個晶圓廠設施本身的成本一樣高。

隨著時間的推移和晶體管的尺寸不斷縮小,建造晶圓廠的成本也隨之上升。

對於現代半導體工廠來說,每個新工藝節點都會使工廠成本增加約 30%。這種增長有兩個主要驅動因素:一是更先進的工藝節點需要更昂貴的設備。例如,ASML 的 EUV 光刻機比它們所取代的深紫外光刻機貴得多;第二個主要成本驅動因素是,隨著晶體管不斷縮小,制造它們需要更多的掩模和工藝步驟。

將晶體管連接在一起需要更多層的金屬線,而FinFET (由從晶圓表面突出的“鰭”制成的晶體管)比它們所取代的更簡單的晶體管需要更多的分層步驟。(然而,EUV 暫時扭轉這一趨勢,因為它可以在一個掩模中完成以前需要兩個或多個掩模完成的工作,從而減少工藝步驟的數量。)更多的層數和更多的工藝步驟意味著更多的設備:如果產品 A的制造步驟是產品 B 的兩倍,如果要保持產量水平不變,則需要兩倍的設備來生產。

但除這兩個因素之外,還有其他成本驅動因素。隨著半導體特征變得越來越小,用於生產它們的矽晶圓也變得越來越大。

20 世紀 70 年代,芯片是在 50 毫米晶圓上生產的,但如今的領先晶圓廠使用更大的 300 毫米晶圓(原本計劃過渡到 450 毫米晶圓,但從未執行),而更大的晶圓往往需要更昂貴的設備。例如,改用 300 毫米晶圓就需要更多地使用自動化材料處理設備,因為晶圓太重,無法用手在 FOUP 中攜帶。反過來,這些處理系統需要更大的結構和更高的潔凈室天花板。

晶圓廠成本不斷增加,導致半導體行業結構發生轉變。當建造晶圓廠的成本較低時,任何芯片生產商都有能力擁有自己的晶圓廠。但隨著晶圓廠成本的增加,由於成本高昂,制造商運營尖端制造設施的負擔變得越來越重,而擁有產量來分攤這些成本的制造商越來越少。

150 毫米晶圓廠的“有效規模”約為每月 10,000 片晶圓,但對於 300 毫米邏輯晶圓廠來說,這一數字將躍升至 40,000 片晶圓。(內存晶圓廠將會更大,每月可生產 12 萬片晶圓。因此,隻有極少數公司(目前是臺積電、三星和英特爾)嘗試運營領先節點,行業已轉向“無晶圓廠”在這種模式下,蘋果和英偉達等公司設計自己的芯片,然後由臺積電等“代工廠”制造。通過匯集許多不同芯片公司的訂單,代工廠可以達到負擔尖端晶圓廠所需的規模。

結論

現代半導體工廠的巨額開支歸結為兩件事的交叉點:

一是半導體工廠是大規模生產工廠,現代“gigafabs”每年生產數億個芯片,每個芯片包含數十億個晶體管。

二是生產半導體需要幾乎深不可測的精度。一年 365 天、每天 24 小時、重復且可靠地在原子水平上操縱大量物質是一項極其昂貴的任務。