閃存芯片的進化方向非常明確,那就是通過更多層地堆疊來實現更快的讀寫速度,同時提高單位面積的存儲容量,降低存儲成本。在ISSCC2023期間,35名SK海力士工程師聯名提交論文,詳細闡述他們是如何攻克300+堆疊的難關。

通過運用TPGM(三重驗證編程)、AUSP(自適應未選串預給電)、PDS(被編程假字符串)、APR以及PLRR(平面級讀取重試)等五項技術,他們實現超過300層的TLC顆粒堆疊。

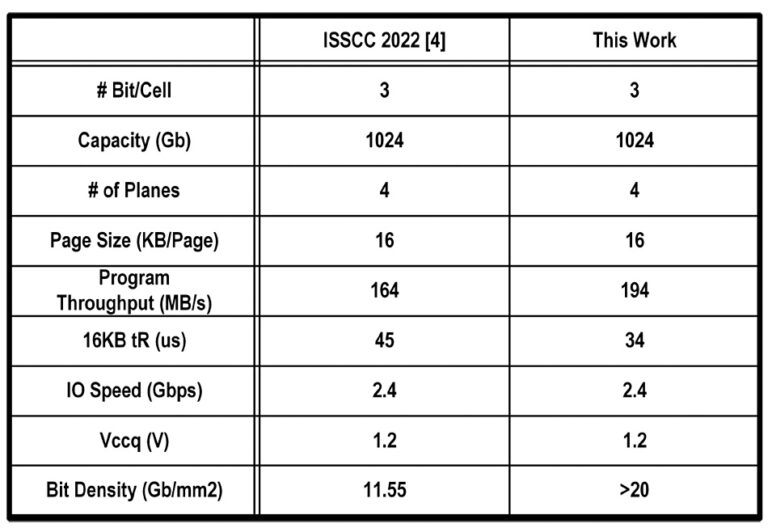

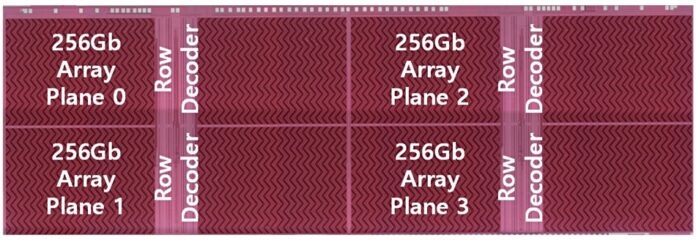

這顆1Tb容量的TLC 3D閃存(3bit/Cell)達到驚人的20Gb/mm2容量密度,寫入速度更是狂飆到194MB/s創紀錄。

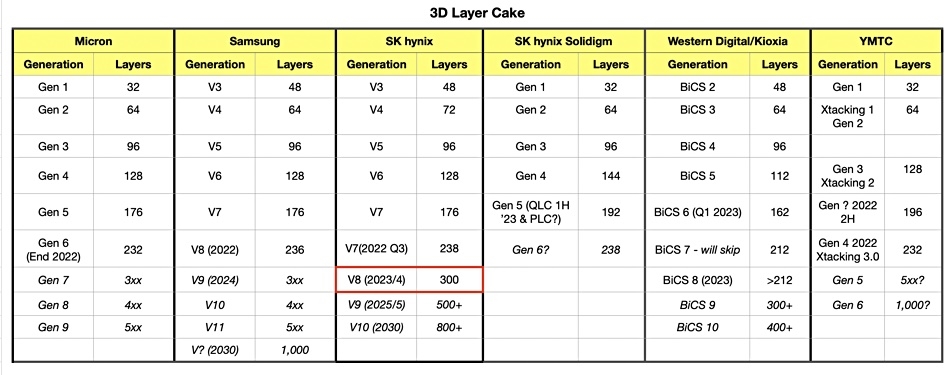

按計劃,SK海力士的300+層TLC將在2024年量產商用。