生產首款1000TBSSD的競賽已經開始,這已不是什麼秘密。在2022年的技術日上,三星公佈雄心勃勃的計劃,到2030年,其最先進的NAND芯片將“堆疊超過1,000層”,這意味著PB級SSD屆時可能問世。去年,該公司曾表示可能能夠更快地交付產品,但這似乎是科技行業的一廂情願。

也就是說,它顯然正在全力推進未來 NAND 芯片的開發。這傢韓國電子巨頭最近宣佈將很快開始量產其最新的 290 層第九代垂直 (V9) NAND 芯片,人們普遍預計接下來將推出令人驚嘆的 430 層第十代 (V10) NAND 芯片年。

因此,雖然我們不太解該公司生產首款 PB SSD 的幕後情況,但網上已經出現一些線索。

今年在檀香山舉行的 VLSI 技術研討會上,韓國科學技術院 (KAIST) 電氣工程系博士生Giwuk Kim將主持一場技術會議。他的研究興趣包括基於鉿的 FE-NAND 存儲器、FeRAM 和內存計算應用,這將是本次會議的重點,題為“In-depth Analysis of the Hafnia Ferroelectrics as a Key Enabler for Low Voltage & QLC 3D VNAND Beyond 1K Layer Experimental Demonstration and Modeling。”

該工作的摘要(劇透警報)由三星電子共同撰寫,內容如下:“我們通過實驗證明金屬帶中電荷捕獲和鐵電 (FE) 開關效應相互作用的顯著性能改進。工程柵極中間層 (BE-G.IL)-FE 溝道中間層 (Ch.IL)-Si (MIFIS) FeFET。具有 BE-G.IL (BE-MIFIS) 的 MIFIS 有助於最大化雙重效應的“正反饋”(Posi.FB.),從而實現低工作電壓 (VPGM/VERS:+17/-15 V)、寬范圍存儲窗口(MW:10.5 V)和 9 V 偏置電壓下的幹擾可忽略不計。此外,我們提出的模型驗證 BE-MIFIS FeFET 的性能增強歸因於增強的 Posi。 FB。這項工作證明,hafnia FE 可以成為擴展 3D VNAND 技術開發的關鍵推動者,而該技術目前正接近停滯狀態。”

目前還不清楚三星將在演示中扮演什麼角色(如果有的話),但該公司並不是唯一一傢探索氧化鉿鐵電體潛力的公司。 Giwuk Kim 的演講是題為“非易失性內存技術 - Hafnia Based Ferroelectrics-1”研討會傢長會議的一部分,該研討會將由三星主要競爭對手 SK 海力士材料開發主管 Deoksin Kil 主持。

01

3D NAND,1000層

據Xtech Nikkei報道,Kioxia 首席技術官 (CTO) Hidefumi Miyajima 表示,該公司計劃到 2031 年批量生產超過 1,000 層的 3D NAND 內存。在東京城市大學舉行的第 71 屆應用物理學會春季會議上的演講中,Miyajima 討論在 3D NAND 器件中實現超過 1000 層的技術挑戰和解決方案。

增加 3D NAND 器件中的有源層數量是當今提高閃存記錄密度的最佳方法,因此所有 3D NAND 制造商都努力每 1.5 到 2 年就推出新的工藝節點來實現這一目標。每個新節點都會帶來一些挑戰,因為 3D NAND 制造商必須增加層數並橫向和縱向縮小 NAND 單元。這個過程要求制造商在每個新節點都采用新材料,這是一項重大的研發挑戰。

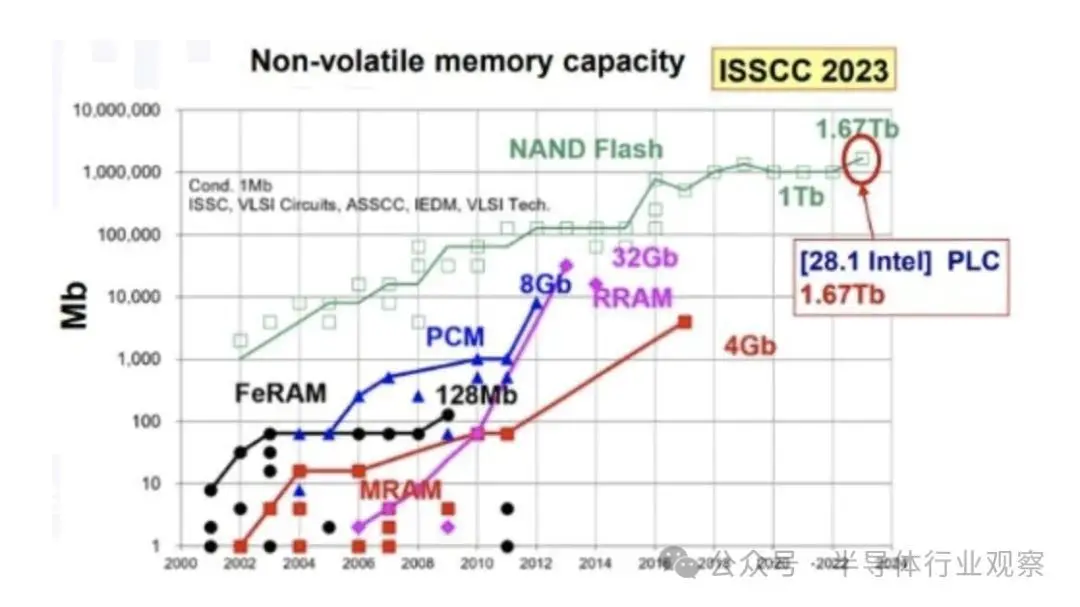

圖1:NAND 閃存公司正在競相開發通過高堆疊增加容量的技術。

2013年前後,NAND Flash的容量提升方式從小型化轉向分層化。目前,各傢公司都在競相量產200層以上的3D NAND(圖1)。小型化的限制是由於器件操作的物理限制和光刻成本的增加,但對於堆疊而言,“如何降低工藝成本已成為與光刻一樣大的問題。”

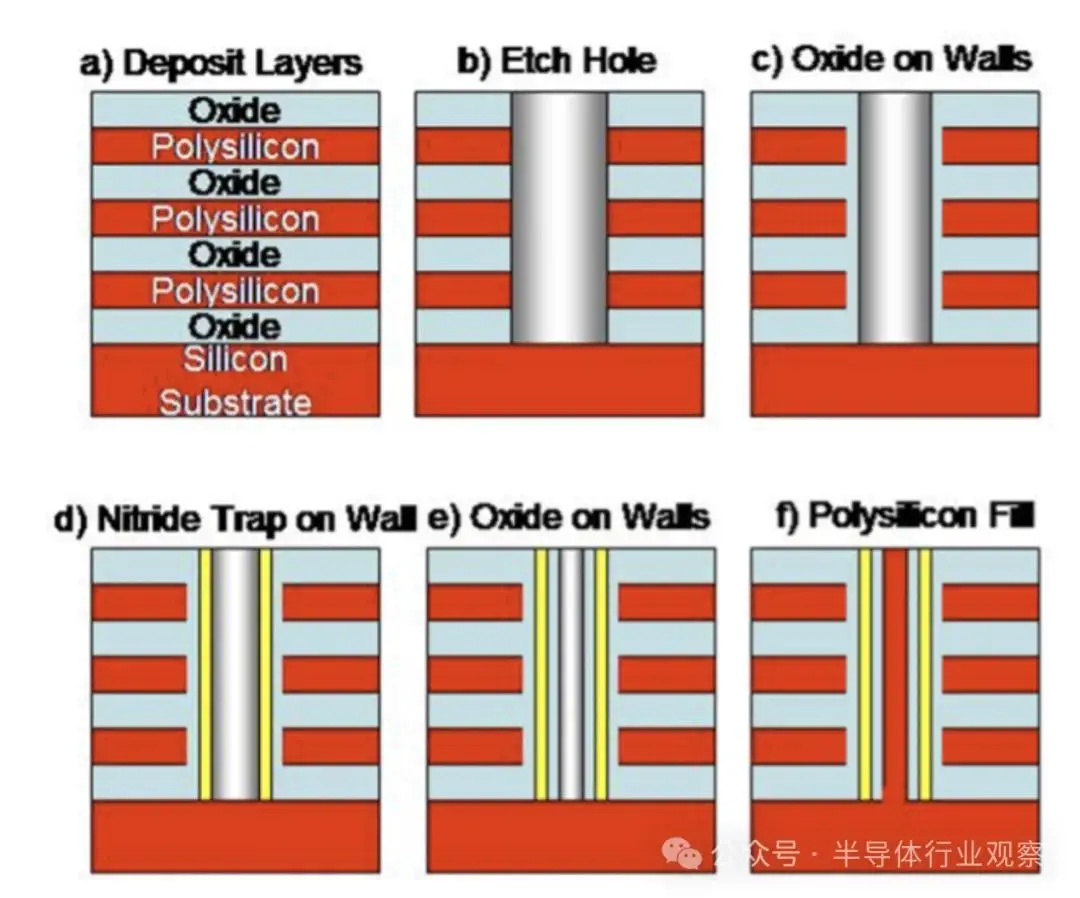

蝕刻工藝對制造成本的影響特別大。3D NAND 的多層薄膜形成後,通過等離子蝕刻產生大量孔(存儲孔),從頂層貫穿底層。該工藝是通過在孔中沉積氧化膜、氮化膜等來制造多層存儲單元。

內存孔的直徑約為100納米,深度為數微米,因此能夠快速、均勻地鉆出大深寬比孔的蝕刻技術至關重要。每 300mm 晶圓上的存儲孔數量達到數萬億個。

這種蝕刻工藝“大約需要一個小時。因為需要時間,所以需要增加設備數量,使其成為(對於3D NAND)成本最高的工藝”。隨著堆疊層數的增加以及存儲孔的深寬比的增加,蝕刻所需的時間呈指數增長,從而增加制造成本。均勻加工難度的增加也往往是降低產量的一個因素。

因此,對於Kioxia的第8代產品,我們沒有一次性構建218層,而是采用分兩步構建的方法。但又增加新的困難,比如需要將下層和上層的內存孔完美對齊。

如今,Kioxia 最好的 3D NAND 器件是第八代 BiCS 3D NAND 存儲器,具有 218 個有源層和 3.2 GT/s 接口(於 2023 年 3 月首次推出)。這一代引入一種新穎的CBA(CMOS直接鍵合到陣列)架構,該架構涉及使用最合適的工藝技術單獨制造3D NAND單元陣列晶圓和I/O CMOS晶圓並將它們鍵合在一起。其結果是產品具有增強的位密度和改進的 NAND I/O 速度,這確保內存可用於構建最好的 SSD。

與此同時,Kioxia 及其制造合作夥伴 Western Digital 尚未披露 CBA 架構的具體細節,例如 I/O CMOS 晶圓是否包括額外的 NAND 外圍電路(如頁緩沖器(page buffers)、讀出放大器和電荷泵)。通過分別生產存儲單元和外圍電路,制造商可以為每個組件利用最高效的工藝技術,隨著行業向串堆疊等方法發展,制造商將獲得更多優勢,串堆疊肯定會用於 1,000 層 3D NAND。

值得註意的是,三星還預計將實現量產級1000層3D NAND。根據2022年9月的報道,該公司目前正在設計第 9 代和第 10 代 V-NAND 並進行原型設計,與當今的技術相比,層密度適當增加。三星目前正在出貨其第七代 176 層 V-NAND,並計劃在今年年底前發佈基於其第八代 230 層設計的 V-NAND 芯片。後者采用 512 Gb 芯片,密度將提高 42%。

但三星正著眼於密度的更大幅度躍升,並預計到 2030 年實現 1,000 層 V-NAND 設計。三星還繼續致力於 QLC(四級單元)技術,希望在提高存儲位的同時提高性能密度。

02

3D-NAND 的層數有限制嗎?

回顧 2D NAND,它采用平面架構,浮動柵極 (FG) 和外圍電路彼此相鄰。2007年,隨著2D NAND的尺寸達到極限,東芝提出3D NAND結構。

三星於 2013 年率先向市場推出所謂的“V-NAND”。

3D 設計引入多晶矽和二氧化矽的交替層,並將浮動柵極替換為電荷陷阱閃存 (CTF)。這些區別既有技術上的,也有經濟上的。FG 將存儲器存儲在導電層中,而 CTF 將電荷“捕獲”在介電層內。由於制造成本降低,CTF 設計很快成為首選,但當然不是唯一的。

IBM 研究員 Roman Pletka 指出:“盡管所有制造商都轉向電荷陷阱單元架構,但我預計傳統浮柵單元在未來仍將發揮不可忽視的作用,特別是對於容量或保留敏感的用例。”

然而,Hynix 表示,盡管采用摩天大樓式堆疊的創新,但第一代 3D NAND 設計仍將外圍電路保留在一側。

最終,3D NAND 供應商將外圍電路移至 CTF 下。用 SK Hynix 的術語來說,它現在是 Periphery Under Cell (PUC) 層。一方面,“4D NAND”比 CTF/PUC NAND 更短、更酷。另一方面,這最終是 3D NAND 的另一種變體,單位單元面積更小。針對較小占地面積的類似設計有不同的商標名稱,例如 Micron 的 CMOS under Array (CuA)。

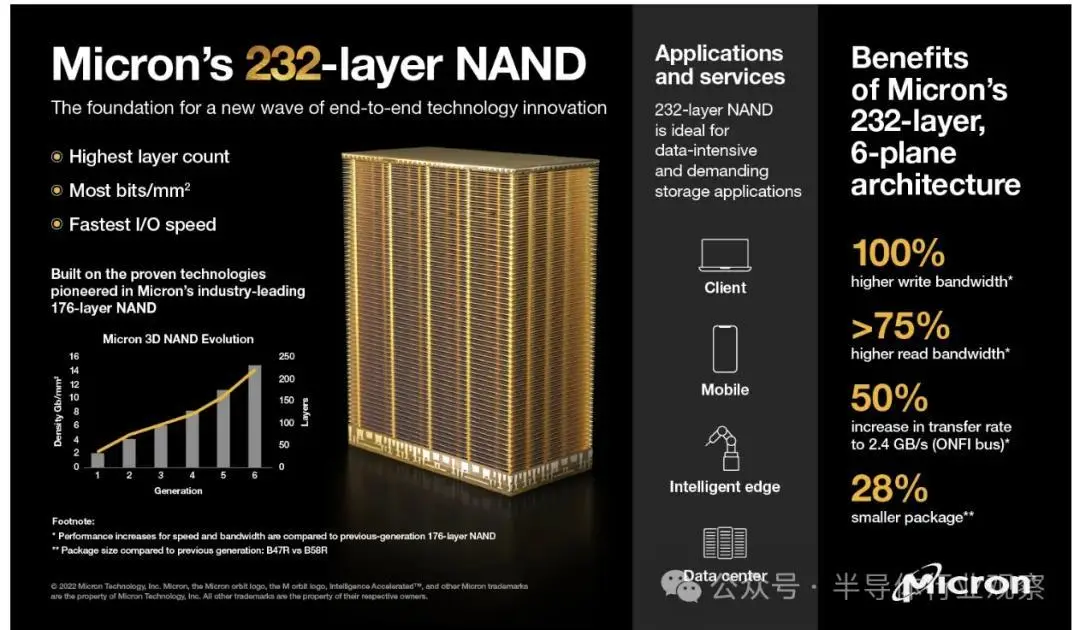

美光科技在 2022 年 7 月下旬宣佈推出 232 層 NAND,並已投入生產,因此獲得吹噓的資本。根據該公司的新聞稿,美光表示,其 232 層 NAND 是存儲創新的分水嶺,也是將 3D NAND 生產擴展到 200 層以上的能力的第一個證明。

美光還聲稱 業界最快的 NAND I/O 速度為 2.4 Gbps,與上一代產品相比,每個芯片的寫入帶寬提高 100%,讀取帶寬提高 75% 以上。此外,232層NAND包含六平面TLC生產NAND,美光表示這是所有TLC閃存中每個芯片最多的平面,並且每個平面都具有獨立的讀取能力。

業內分析人士認為,這可能是此次公告中最令人印象深刻的部分。由於有六個平面,該芯片的表現就像是六個不同的芯片一樣。

03

制造:優勢與挑戰

在早幾年的 IEEE IEDM 論壇上,三星的 Kinam Kim 發表主題演講,他預測到 2030 年將出現 1,000 層閃存。這可能聽起來令人頭暈,但這並不完全是科幻小說。Imec 存儲內存項目總監 Maarten Rosmeulen 表示:“相對 NAND 閃存的歷史趨勢線而言,這一速度已經放緩。” “如果你看看其他公司,比如美光或西部數據,他們在公開聲明中提出的內容,你會發現他們的速度甚至比這還要慢。不同制造商之間也存在一些差異——看起來他們正在延長路線圖,讓它放慢速度。我們相信這是因為維持這個空間的運轉需要非常高的投資。”

盡管如此,競爭風險仍然足夠高,這些投資是不可避免的。“前進的主要方式,主要的乘數,是在堆棧中添加更多層,”Rosmeulen 說。“幾乎沒有空間進行 XY 收縮並縮小內存空洞。這很難做到。也許他們會在這裡或那裡擠壓百分之幾,將孔放得更近,孔之間的縫隙更少等等。但這並不是最大的收益所在。如果你能繼續堆疊更多的層,密度隻能以目前的速度顯著提高。”

圖 2:NAND 制造中的 3D 步驟

除整個過程的核心不可避免的問題之外,進一步堆疊似乎是合理的。

“主要挑戰在於蝕刻,因為你必須蝕刻具有非常高深寬比的非常深的孔,”Rosmeulen 說。“如果你看看上一代的 128 層,這大約是一個 6、7 或 8 微米深的孔,直徑僅為 120 納米左右,具有極高的縱橫比,或者可能更高一點,但並非如此很多。蝕刻技術取得進步,可以一次性蝕刻更深的孔,但速度不會更快。您無法提高蝕刻速度。因此,如果工藝流程以沉積和蝕刻為主,並且這些工藝步驟沒有提高成本效率,那麼添加更多層就不再能夠有效地降低成本。”

蝕刻也隻是多個步驟之一。“除蝕刻之外,您還需要用非常薄的介電層上下均勻地填充這個孔,”Synopsys 的 Lin 說。“通常,由於晶圓的化學性質,沉積幾納米的層並不容易。在這裡,他們必須一路向下才能填滿。有亞原子層沉積方法,但仍然具有挑戰性。另一個巨大的挑戰是壓力。如果您構建如此多的層並經歷一些蝕刻/沉積/清潔/熱循環,則可能會導致局部和全局應力。在局部,因為鉆孔後,您需要在整個堆棧上切出一條非常深的溝槽。它變成一座非常高的摩天大樓,而且搖搖欲墜。如果你開始進行一些清洗或其他過程,很多事情都可能發生,導致兩座摩天大樓相互倒塌。那麼你就失去收益。通過將如此多的材料相互疊加並切割不同的圖案,這可能會產生全局應力並導致晶圓翹曲,這將使其無法在晶圓廠中進行處理,因為晶圓必須是平坦的。

請記住,蝕刻是穿過不同材料層的。

Objective Analysis 的 Handy 表示,三星的解決方案是創建極薄的層。“這對整個行業很有用,因為每個人都使用幾乎相同的工具來創建這些東西。”

04

結論

2016年,專傢指出,由於技術問題,3D NAND可能會在300層或接近300層時失去動力。這似乎已被今天的謹慎樂觀所取代。

“[SK Hynix 的 238 層之後]我預計未來幾年層數將以大致相同的速度增加,”IBM 的 Pletka 表示。“然而,從技術角度來看,由於高深寬比蝕刻工藝,增加層數面臨挑戰,而且資本支出也面臨挑戰,因為制造芯片的時間隨著層數的增加而增加。這就是為什麼我們將看到新的縮放方向,通過制作更薄的層、橫向縮放(例如更密集地放置垂直孔)以及使用更有效的佈局(例如共享位線和邏輯縮放)(例如,使用分柵架構或存儲更多每單元位數)。借助這些技術,預計 NAND 閃存的存儲密度至少在未來 5 到 10 年內將繼續以類似的速度增長。”

其他人也同意。Objective Analysis 首席分析師吉姆·漢迪 (Jim Handy) 表示:“當人們說我們無法超越這麼多層時,這實際上是沒有物理限制的。” “在半導體領域,總是有人說我們做不到。我們無法進行 20 納米以下的光刻。現在,他們正在研究 1 納米。三星談到 1,000 層。20年後,我們可能會嘲笑我們曾經認為這已經很多。”