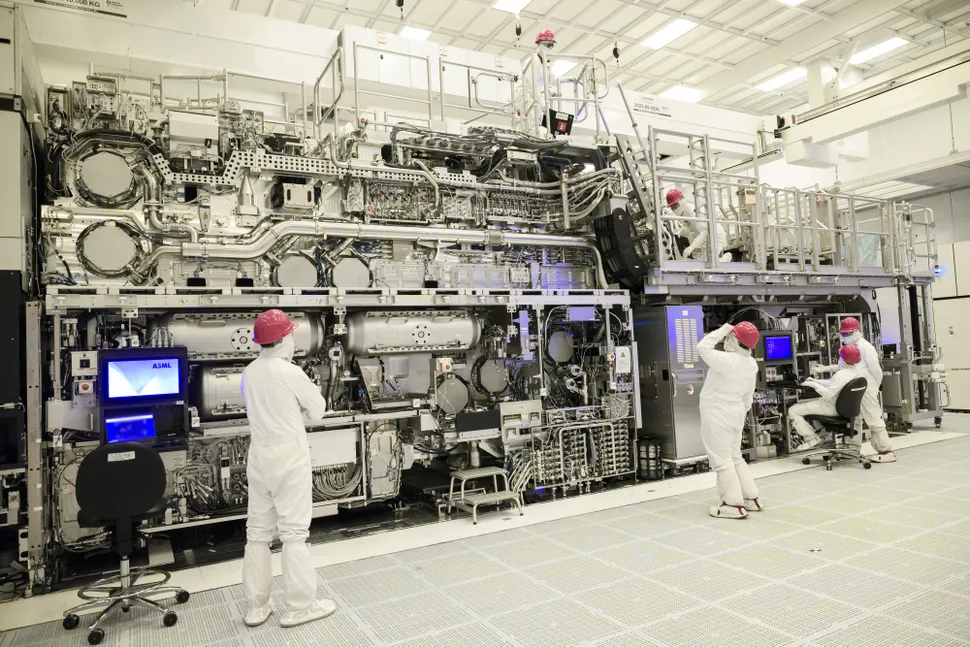

英特爾已經完成第一臺高數值孔徑(HighNA)極紫外光刻掃描儀的組裝,英特爾院士MarkPhillips(馬克·菲利普斯)討論進展和前景。TwinscanEXE:5000的供應商ASMLHoldingNV(荷蘭Veldhoven)必須完成掃描儀的集成和校準,該掃描儀位於俄勒岡州希爾斯伯勒的英特爾研發基地D1X。

英特爾院士兼英特爾代工廠邏輯技術開發光刻、硬件和解決方案總監 Mark Phillips 表示,英特爾將於 2024 年晚些時候開始該機器的開發工作。

英特爾預計將使用 0.33NA EUV 和 0.55NA EUV 以及其他光刻工藝來開發和制造先進芯片,從 2025 年英特爾 18A 的產品驗證點開始。根據顯示的材料,這將在 2026 年轉移到英特爾的 14A 工藝。

菲利普斯在與記者討論高數值孔徑 EUV 的電話會議上發表講話。高數值孔徑 EUV 預計能夠打印比現有 EUV 工具小 1.7 倍的特征。這將實現 2D 特征縮放,從而使密度提高 2.9 倍。與 0.33NA EUV 相比,High NA EUV(或 0.55NA EUV)可以為類似特征提供更高的成像對比度,從而減少每次曝光的光量,從而減少打印每層所需的時間並增加晶圓產量。

菲利普斯表示,他預計高數值孔徑能夠解決低至 1 埃及以下基本上是單原子尺寸的尖端芯片制造問題。

“它[高數值孔徑]將持續幾代。節點的數量部分取決於您如何定義節點。我預計至少有三代的High NA。” Phillips 表示,他預計短期內不會將 EUV 波長從目前的 13.5nm 縮短為光刻技術的前進方向。

“轉向 6.7nm 波長會帶來很多其他問題,”菲利普斯說。他說,光學要求“爆炸”,意味著它們占用更多的空間。“下一個討論可能是關於超 NA,”菲利普斯說,他表示 NA 達到 0.75 存在一定的可能性。“NA 為 0.75 的半場工具可以在很大程度上利用迄今為止開發的技術並在類似的系統尺寸下完成。”

然而,半場尺寸(half-field size)也表明高數值孔徑 EUVL 的問題之一,這可能會影響小芯片組件封裝的采用。

隨著高數值孔徑光學器件的實施,由於使用變形透鏡陣列,標線的最大視場尺寸減小。具體來說,標準掩模版限制從傳統 EUVL 的 26mm x 33mm 減半至 26mm x 13.5mm。這種減少是高數值孔徑 EUV 光刻分辨率能力提高的結果。

利普斯被問及縮小掩模版尺寸是否意味著更小的芯片。

菲利普斯說:“分解、更小的芯片和小芯片是一種方法。但一些客戶仍然需要更大的芯片,因此我們將提供“縫合”功能。目前對於設計師來說還不是完全透明的。”菲利普斯補充說,英特爾正在與 EDA 公司合作,嘗試使其更容易實施。

他補充說,重要的是能夠將設計元素縫合在一起以創建單個模具,以獲得昂貴工具的最大利用率。

據稱,High NA EUV曝光機的價格約為3.8億美元,是上一代低NA EUV曝光機約1.8億美元的兩倍多。