在人工智能飛速發展的時代,對更強大計算能力的需求已成為未來進步的關鍵。因此,我們將目睹半導體晶體管數量的急劇增加,到本十年末有可能突破一萬億個大關。當半導體專傢們討論未來的進展時,GPU中的晶體管數量是一個令人感興趣的話題,因為它們是半導體性能和效率的重要決定因素。

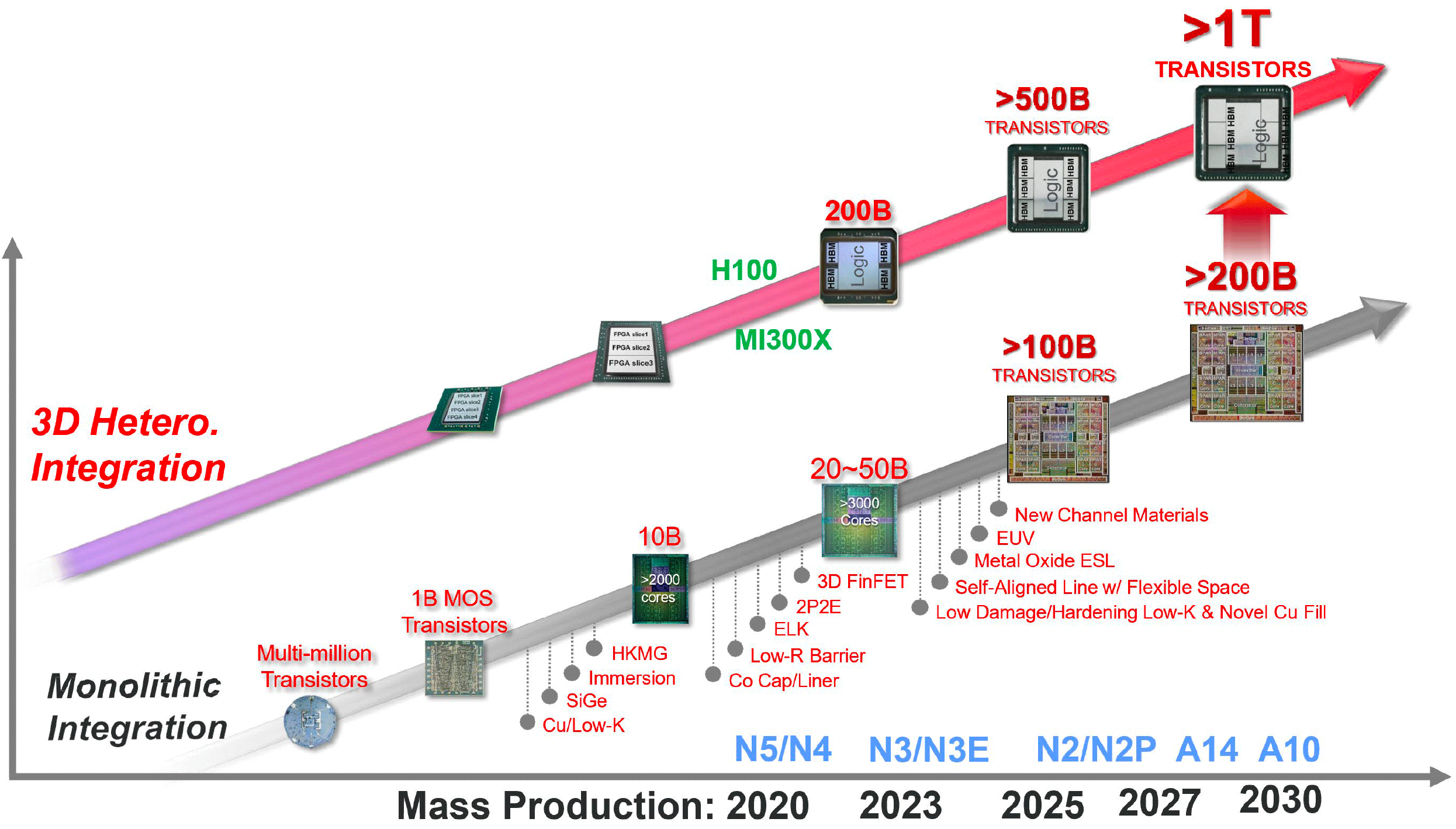

臺積電等公司對半導體集成表現出極大的樂觀,計劃在未來十年內實現萬億個晶體管的目標,並將其視為邁向未來的重要一步。

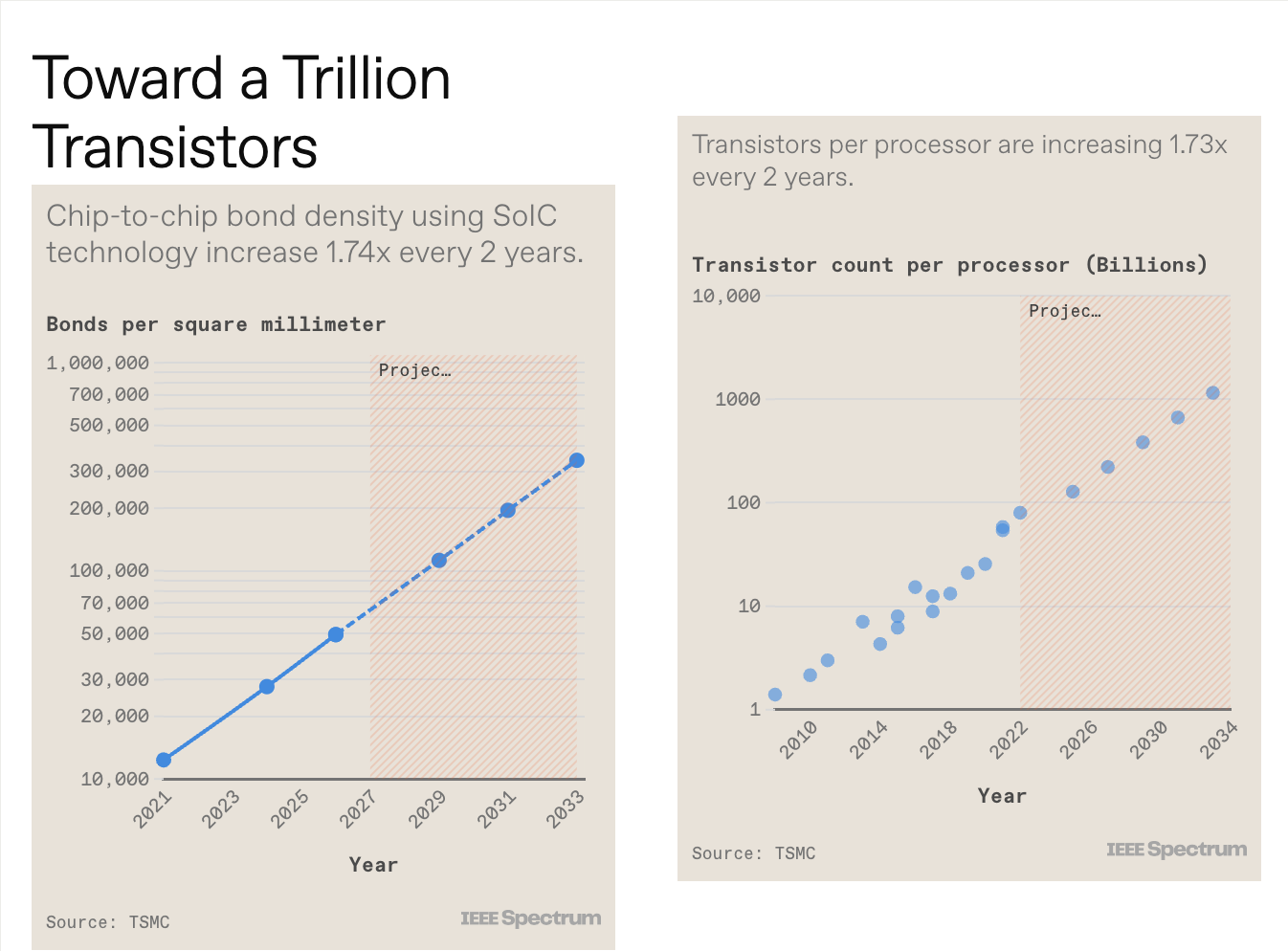

據他們稱,3D SoIC技術的出現將對晶體管的集成起到至關重要的作用,因為現在光刻工具的能力比以往任何時候都強,使業界可以將多個芯片連接到一個更大的中間件上。

目前,NVIDIA最近公佈的 Blackwell GPU 架構的晶體管數量為 2,080 億個,這意味著未來十年內該行業的晶體管數量有望達到這個數字的 5 倍。

此外,互聯技術也將在其中發揮重要作用,因為通過 CoWoS 等先進封裝技術實現 2.5D 或 3D 集成後,專傢們可以在每個系統中堆疊數量更多的晶體管,而不僅僅是將它們安裝到單個芯片上。

同樣,臺積電在最近舉行的 IEDM 大會上透露,該公司計劃到 2030 年通過 3D 異質集成技術提供超過一萬億個晶體管,這意味著在性能提升方面,預計未來會有顯著的數字增長,因為半導體行業的發展遠不止節點縮小這麼簡單。

對我們和半導體行業來說,未來確實充滿希望,隨著人工智能浪潮的到來,創新之火將蔓延到每個技術領域,最終為消費者和客戶市場打開新的大門。

您可以從IEEE Spectrum解更多。