讓我們先忘掉芯片的縮小,專註於集成電路技術的進步。臺積電公佈下一代SoW封裝的龐大計劃,從而計劃實現這一目標。臺積電將下一代"SoW"芯片封裝視為邁向未來的關鍵因素,這意味著芯片可能變得比以往任何時候都大!

在深入解臺積電披露的信息之前,我們先來談談內插器芯片。想象一下你手中的芯片,假設它是一個功能強大的芯片,如果您渴望從單個芯片中獲得更多的功能,那麼業界不會走創新路線,而是會將多個芯片相互連接,以實現功率的累積。為此,帶內插器的微電子電路封裝技術就派上用場。

在人工智能和高性能計算時代,計算能力變得比以往任何時候都更有必要,芯片封裝在推動行業發展方面發揮至關重要的作用,而且看起來它還將繼續發揮作用。

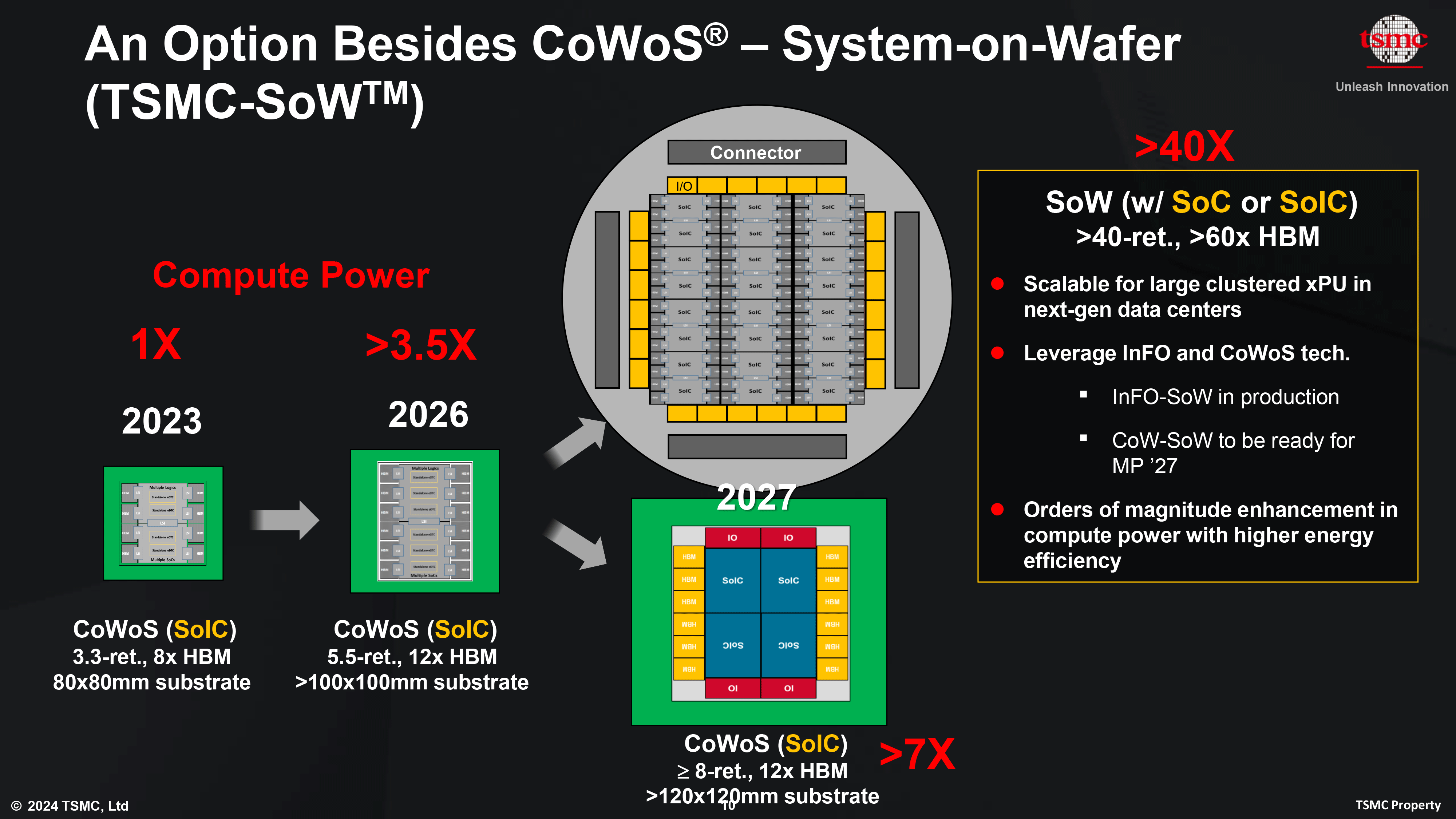

在臺積電的技術研討會上,該公司展示其 A16 工藝,並透露許多其他細節。目前,傳統的 CoWoS 封裝允許市場將臺積電的微粒極限提高 3.3 倍。這裡的微粒限制是指應用於標準微粒尺寸限制的乘數,以確定有效可用面積;簡單地說,乘數越大,效果越好。

更有趣的是,臺積電透露,其即將推出的 CoWoS-L 封裝將於 2026 年亮相,計劃采用 5.5 倍於臺積電光罩極限的封裝,這意味著它將采用 12 個 HBM 內存堆棧,同時采用更大的基板(100×100 毫米)。憑借這一創新,這傢臺灣巨頭計劃將芯片的計算性能提高到上一代產品的 3.5 倍,而這僅僅是個開始,因為該公司對未來還有更大的計劃。

到 2027 年,臺積電計劃推出 8 倍微粒極限的 CoWoS,支持更大的 120mm x 120mm 基板,集成四種不同的 SoIC,為後續市場奠定新的基調。此外,臺積電還提到專門的 SoW 封裝標準,據說該標準將擁有 40 倍的微粒極限和 60 個 HBM 堆棧,並明確針對未來的數據中心集群。

芯片封裝技術的進步表明,工藝縮減並不是決定未來計算能力的唯一因素。現代發展已經向我們表明,CoWoS 將在塑造人工智能和高性能計算產業的未來中發揮至關重要的作用。