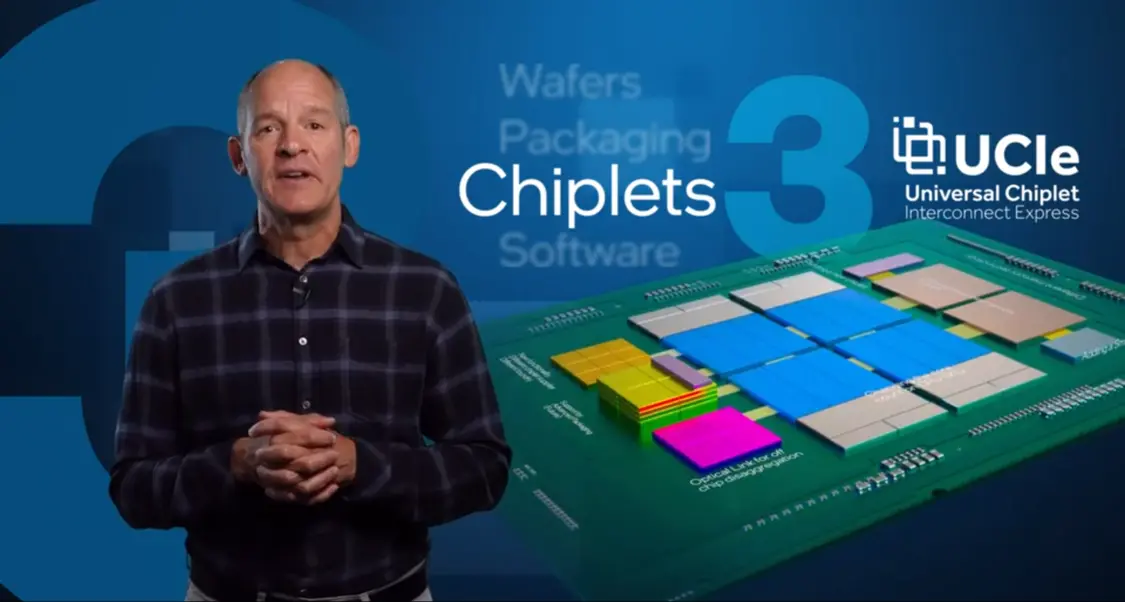

靜水深流式的代工市場最近格外不平靜。在三星豪言2027年將量產1.4nm、臺積電或將重返半導體王座之後,英特爾也拋出“系統級代工”來強力助攻IDM2.0。在前不久舉行的英特爾On技術創新峰會上,CEO帕特·基辛格宣稱,英特爾代工服務(IFS)將開創“系統級代工”的時代,不同於僅向客戶提供晶圓制造能力的傳統代工模式,英特爾將提供涵蓋晶圓、封裝、軟件和Chiplet(芯粒)的全面方案。

基辛格著重表示,“這標志著從系統級芯片(system-on-a-chip)到系統級封裝(system in a package)的范式轉移。”在英特爾這一巨輪加速向IDM2.0挺進之後,近來動作不斷:無論是開放x86,加盟RISC-V陣營,還是收購高塔、擴充UCIe聯盟、宣佈數百億美元的代工產線擴建計劃等等不一而足,顯現出要在代工市場三分天下有其一的野望。

而今,再祭出系統級代工“大招”的英特爾會如願在“三皇”會戰中增加更多籌碼嗎?

大勢使然

系統級代工概念的“問世”,其實早已有跡可尋。

在摩爾定律放緩之後,實現晶體管密度、功耗、尺寸之間的平衡面臨更多的挑戰,而新興應用對高性能大算力以及異構集成的芯片需求有增無減,驅動著業界探尋新的解決之道。

借助於設計、制造、先進封裝以及近年來興起的Chiplet等,來實現摩爾定律的“續命”以及芯片性能的持續躍遷,看起來已成共識。特別是在未來制程微縮受限的情況下,Chiplet與先進封裝搭配將會是突破摩爾定律的解法。

而代工廠來充當聯接設計、制造和先進封裝的“主力”,顯然有著先天的優勢和能夠盤活的資源。意識到這一大勢,不論是臺積電、三星還是英特爾等這些頂級玩傢均在著力佈局。

在一位半導體代工行業資深人士看來,系統級代工是未來代工的必然趨勢,相當於泛IDM模式的擴展,類似於CIDM,但差異在於CIDM是不同公司通過一個共同的任務來銜接,而泛IDM則是將不同任務整合為客戶提供一個Turnkey Solution。

英特爾方面在接受集微網采訪時表示,從系統級代工的四大支撐體系來看,英特爾均具備優勢技術的積淀。

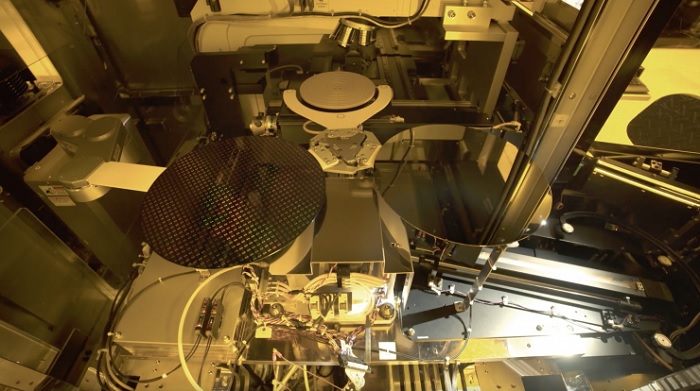

在晶圓制造層面,英特爾開發如RibbonFET晶體管架構和PowerVia供電等創新技術,並在穩步實現在四年內推進五個制程節點的計劃。英特爾還可提供EMIB和Foveros等先進封裝技術,以助力芯片設計企業整合不同的計算引擎和制程技術。而芯粒模塊化的部件為設計提供更大的靈活性,驅動整個行業在價格、性能和功耗方面進行創新。英特爾致力於構建UCIe聯盟助力來自不同供應商或不同制程的芯粒更好地協同工作。在軟件方面,英特爾的開源軟件工具OpenVINO和oneAPI可加速產品的交付,並使客戶能夠在生產前測試解決方案。

憑借系統級代工的四大“護法”,英特爾展望,單顆芯片上集成的晶體管將從目前的1000億個大幅擴展至萬億級別,基本可成定局。

“可以看到英特爾的系統級代工目標契合IDM2.0的戰略,且有相當的勢能,將為英特爾未來的發展打下基石。”上述人士進一步表示對於英特爾的看好。

聯想到以“一站式芯片方案”揚名立萬的聯發科,再到如今“一站式制造”的系統級代工新范式,代工市場或將迎來新的巨變。

勝算籌碼

祭出系統級代工這一大招兒,英特爾其實已然做諸多鋪墊。除卻上文提及的各種創新加成之外,還要看到為系統級封裝新范式所付出的諸多努力和整合力道。

半導體行業人士陳啟分析,從現有資源儲備來看,英特爾擁有完整的x86架構的IP,這是它的底蘊,同時英特爾有PCIe、UCle等高速SerDes類接口IP,可利用這一技術更好地和英特爾核心CPU做Chiplet的組合和直連。而且,英特爾又掌控PCIe技術聯盟標準的制定,而PCIe基礎上發展起來的CXL聯盟和UCle標準也是由英特爾主導,相當於英特爾既掌握核心IP,又掌握非常關鍵的高速SerDes技術和標準。

“英特爾的混合封裝技術、先進工藝能力並不弱,如果能和它的x86 IP內核以及UCIe相結合,確實能在系統級代工時代擁有較多的資源和話語權,並打造出一個全新的英特爾,持續保持強大。”陳啟告訴集微網。

要知道,這都是英特爾的看傢本領,之前是不會輕易示人的。

“由於過去在CPU領域的強勢,系統內關鍵資源——內存資源被英特爾牢牢把控,系統內其他芯片想要使用內存資源,必須通過CPU獲得,因此英特爾可通過此舉限制其他公司的芯片,過去業界對這一‘間接’的壟斷行為怨聲載道。”陳啟解讀說,“但隨著時代的發展,英特爾感受到四面八方的競爭壓力,因而主動求變,將PCIe技術開放出來,相繼成立CXL聯盟和UCle聯盟,相當於主動把蛋糕放在桌子上。”

行業看來,英特爾在IC設計、先進封裝領域的技術跟佈局仍然十分紮實。以賽亞調研(Isaiah Research)認為,英特爾走向系統級代工模式,是希望整合這兩大方面的優勢與資源,通過從設計到封裝一條龍的概念,差異化其他晶圓代工廠,以在未來代工市場獲得更多訂單。

“以這樣Turnkey solution的方式,對於小型初級開發而且研發資源不足的公司是相當有吸引力的。”以賽亞調研還看好英特爾此舉對中小客戶的吸引力。

對於大客戶,有行業專傢直言,英特爾系統級代工最現實的利好還在於可拓展與部分數據中心客戶如Google、亞馬遜等的雙贏合作。

“一是英特爾可授權他們在自己的HPC芯片中使用英特爾X86架構的CPU IP,有利於保持英特爾CPU領域的市場份額。二是英特爾可提供UCle之類的高速接口協議IP,更加方便客戶將其他功能IP整合。三是英特爾提供完整平臺來解決流片、封裝的問題,形成最終英特爾深入參與的亞馬遜版本Chiplet方案芯片。這對英特爾來說應是一個較完美的商業方案。”上述專傢進一步補充。

仍需補課

但做代工需要提供一攬子平臺開發工具,以及樹立“客戶至上”的服務理念,從英特爾以往歷史來看,也曾嘗試過代工,但結果也不盡人意。借助系統級代工盡管能助力其實現IDM2.0的宏願,但隱形的挑戰依然要著力攻克。

“正如羅馬不是一日建成的,代工和封裝不是說技術強大就萬事大吉的事情,從IDM轉型代工,對於英特爾來說,最大挑戰仍是代工文化。”陳啟告訴集微網。

陳啟進一步指出,如果說制造、軟件等生態英特爾還可通過砸錢、技術轉讓或是開放平臺模式來搞定的話,英特爾最大的挑戰是要從體系上構建代工文化,要學會與客戶溝通,為客戶提供所需的服務,滿足客戶差異化的代工需求。

對此以賽亞調研則認為,因為英特爾唯一需要補足的是晶圓代工這部分的能力,相比臺積電有持續且穩定的主要客戶與產品協助提升每段制程良率,英特爾多半隻生產自傢產品,在產品類別與產能有限的情況下,英特爾芯片制造的優化能力有限。通過系統級代工模式,英特爾有機會通過設計、先進封裝、芯粒等技術吸引部分客戶,從少量多元的產品一步步提升晶圓制造的能力。

此外,先進封裝和Chiplet作為系統級代工的“流量密碼”,也面臨各自的難關。

以系統級封裝為例,從其涵義來看,相當於晶圓產出之後要實現不同Die之間的整合,但這殊非易事。以臺積電為例,從最早為蘋果做方案到後來為AMD做代工,臺積電在先進封裝技術方面花費多年時間,並推出多個平臺,如CoWoS、SoIC等,但到最後多數依然是一對一定制化封裝服務,並不是傳言中為客戶提供“芯片像搭積木一樣”高效的封裝方案。

最終,臺積電將各種封裝技術整合後推出3D Fabric代工平臺,同時抓住機會參與UCle聯盟的組建,想方設法將自己的標準和UCIe標準打通,有望後續“搭積木”的推進。

芯粒結合的關鍵在於統一“語言”,即標準化Chiplet接口。為此英特爾也再次揮舞起影響力大旗,以PCIe標準為基礎著力為芯片到芯片互連建立起UCIe標準。

顯然這還需要時間讓標準“通關”。The Linley Group總裁兼首席分析師Linley Gwennap在接受集微網采訪時就提出,業界真正需要的是將芯粒連接在一起的標準方式,但各公司需要時間來設計新的芯粒以滿足新興標準。目前雖已取得一些進展,但仍需要2-3年的時間。

一位半導體資深人士從多維角度表達疑慮,英特爾在2019年退出代工服務不到三年重返,試圖從IDM轉型打造新的服務模式,能否再被市場接受,需時間觀察。從技術來看,英特爾2023年預計推出的下一代CPU在制程和存儲容量、I/O功能等方面仍較難展現優勢。此外,以往英特爾的制程藍圖有過幾次推遲的記錄,而現在同時要進行組織重組、技術提升、市場競爭、建廠等多項艱難任務,相較過去的技術挑戰,似乎更增添未知的風險。特別是英特爾能否在短期內建立起新型系統級代工模式的供應鏈,亦是一大考驗。