近日,國傢知識產權局公佈華為技術有限公司的多項新專利,其中一項專利號CN117751427A的涉及到“自對準四重圖案化(SAQP)半導體裝置的制作方法以及半導體裝置”,也就是江湖傳聞已久的多重曝光芯片制造工藝。傳統的芯片制造方法嚴重依賴極其復雜、精確的掩膜圖案來蝕刻芯片電路,而隨著半導體工藝日益復雜化,所面臨的挑戰也越來越嚴峻,代價越來越高。

比如為造出2nm級工藝芯片,ASML已經打造0.55 NA的新一代EUV極紫外光刻機,價格高達驚人的4億美元左右。

極其復雜的現代光刻機的一小部分

在受到外部條件嚴重制約的情況下,以華為為代表的國內半導體企業已經不可能接觸到這些尖端工藝,隻能另辟蹊徑,比如先進封裝技術,比如多重曝光技術。

簡單地說,多重曝光就是將芯片電路掩膜圖案的蝕刻分成多次完成,可以使用相對落後的技術和設備,達成和更先進工藝類似甚至更先進的結果,比如用7nm設備造出5nm芯片。

其實,多重曝光也不是新鮮事物,半導體巨頭們都嘗試過,但它太過於復雜,需要執行的步驟更多,良品率和質量都難以保障。

比如說,Intel第一代10nm工藝就嘗試過多重曝光,最終也沒能成功,對應的處理器(Cannon Lake)最終被迫取消,第二代成功量產但性能也達不到要求,頻率根本就上不去,甚至無法用於桌面臺式機。

再比如,Intel即將量產的18A 1.8nm工藝,就因為等不到ASML的新一代高NA光刻機,隻能使用現有設備加雙重曝光來實現。

華為這項專利早在2021年9月就申請,正是華為被美國宣佈制裁後的幾個月。

顯然,華為早就有技術儲備,在危難時刻幾乎立即就開始行動,深入相關研究,如今專利公開則意味著華為和相關行業夥伴已經取得實質性的突破,甚至可能已經投入實用!

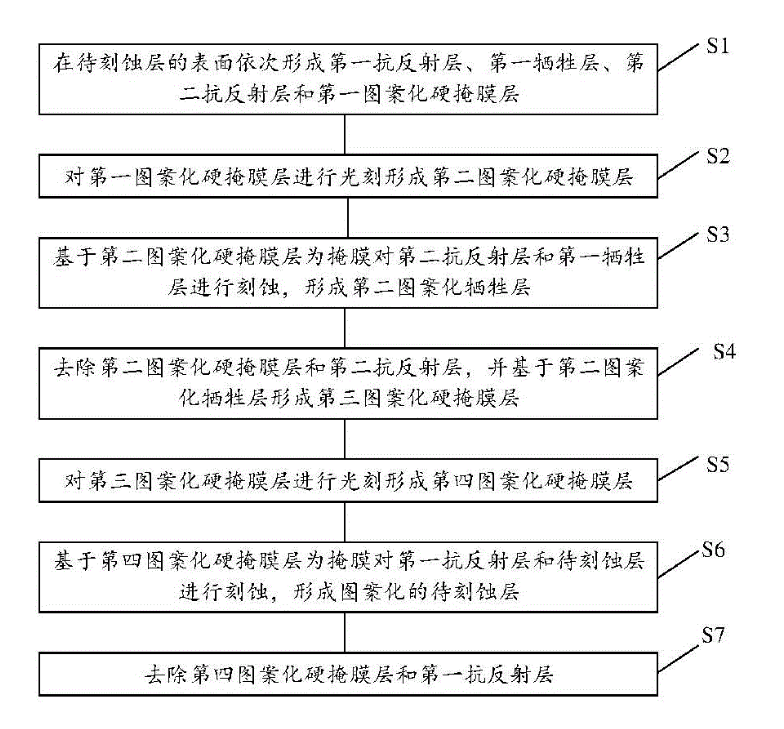

華為這次公開的專利顯示,其自對準四重圖案化工藝可以分為七個步驟:

1、在待刻蝕層的表面依次形成第一抗反射層、第一犧牲層、第二抗反射層和第一圖案化硬掩膜層;

2、對第一圖案化硬掩膜層進行光刻形成第二圖案化硬掩膜層;

3、基於第二圖案化硬掩膜層為掩膜對第二抗反射層和第一犧牲層進行刻蝕,形成第二圖案化犧牲層;

4、去除第二圖案化硬掩膜層和第二抗反射層,並基於第二圖案化犧牲層形成第三圖案化硬掩膜層;

5、對第三圖案化硬掩膜層進行光刻形成第四圖案化硬掩膜層;

6、基於第四圖案化硬掩膜層對第一抗反射層和待刻蝕層進行刻蝕,形成圖案化的待刻蝕層。

7、去除第四圖案化硬掩膜層和第一抗反射層。

也就是說,華為把傳統一次完成的工作拆分成四次,需要多達四層蝕刻,其難度可想而知。

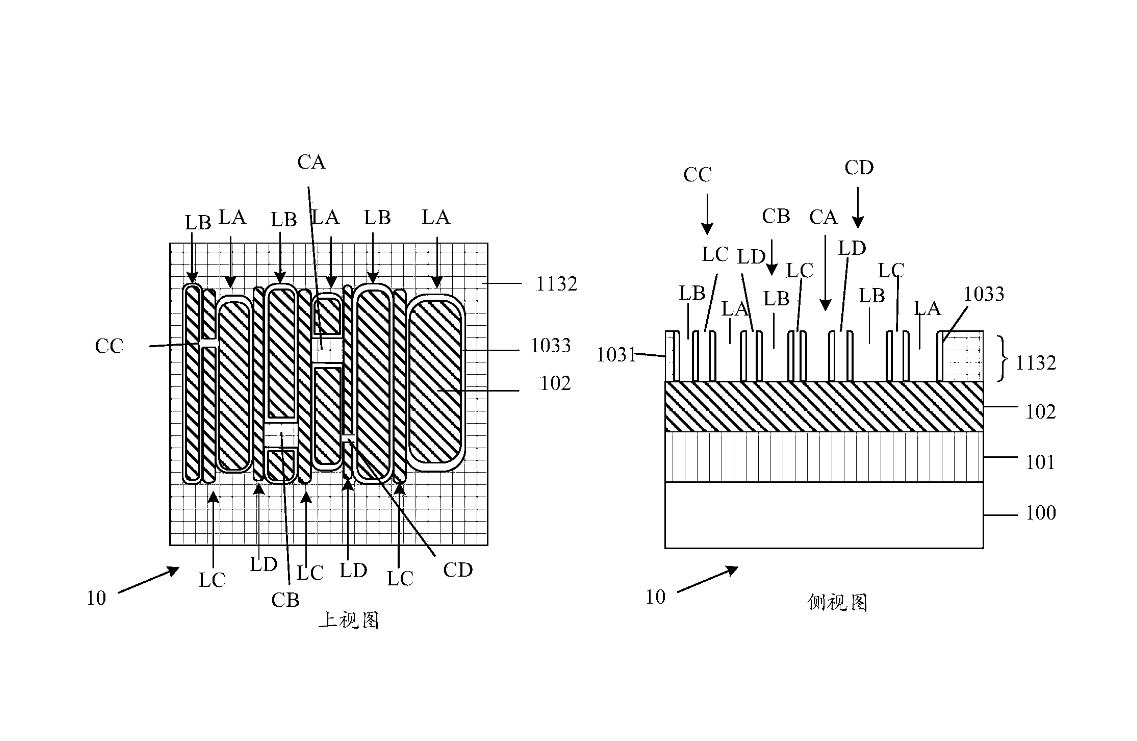

華為在專利中表示:“實施本申請實施例,可以提高電路圖案設計的自由度。”

外媒猜測,華為應該是和中芯等聯合搞定的自對準四重圖案化技術,完全可以造出5nm工藝的芯片。