Intel一直在積極推進四年五代工藝節點的戰略,2021-2024年間將陸續投產7、4、3、20A、18A。其中,20A、18A將邁入埃米時代,大致可以立即為2nm、1.8nm,前者將追平臺積電,後者則最終實現反超。

Intel 20A工藝將引入兩種全新的工藝,PowerVia背部供電、RibbonFET全環繞柵極晶體管。

PwoerVia技術將傳統位於芯片正面的供電層改到背面,與信號傳輸層分離,通過一系列TSV矽穿孔為芯片供電,可以大大降低供電噪聲、電阻損耗,優化供電分佈,提高整體能效。

計劃6月11-16日舉辦的VLSI Symposium 2023研討會上,Intel將首次展示PowerVia技術,不過用的不是20A工藝,而是基於Intel 4工藝的一顆測試芯片,架構則是E核。

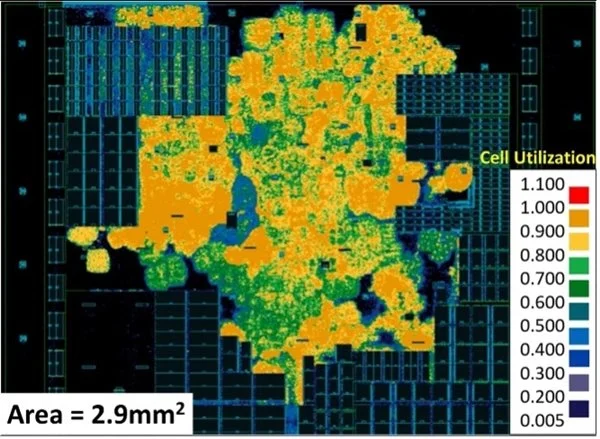

這顆核心的面積僅為2.9平方毫米,得益於PowerVia技術,大部分區域的標準單元利用率都超過90%(圖中橙色區域),其餘的也基本都在80%之上(圖中綠色區域)。

同時,PowerVia技術還帶來超過5%的頻率提升,吞吐時間略高但可以接受,功耗發熱情況符合預期。

除用於自傢產品,Intel也將使用PowerVia技術為客戶代工,這也是提前展示其能力的一個原因。