AMD的銳龍7000X3D系列第二次集成3DV-Cache堆疊緩存,雖然官方說和銳龍75800X3D上的沒有太大區別。但實際上,還是有很多不一樣的。銳龍75800X3D上堆疊的64MB3D緩存采用與CCD部分相同的7nm工藝,面積41平方毫米,晶體管數量47億個,密度為1.146億個/平方毫米。

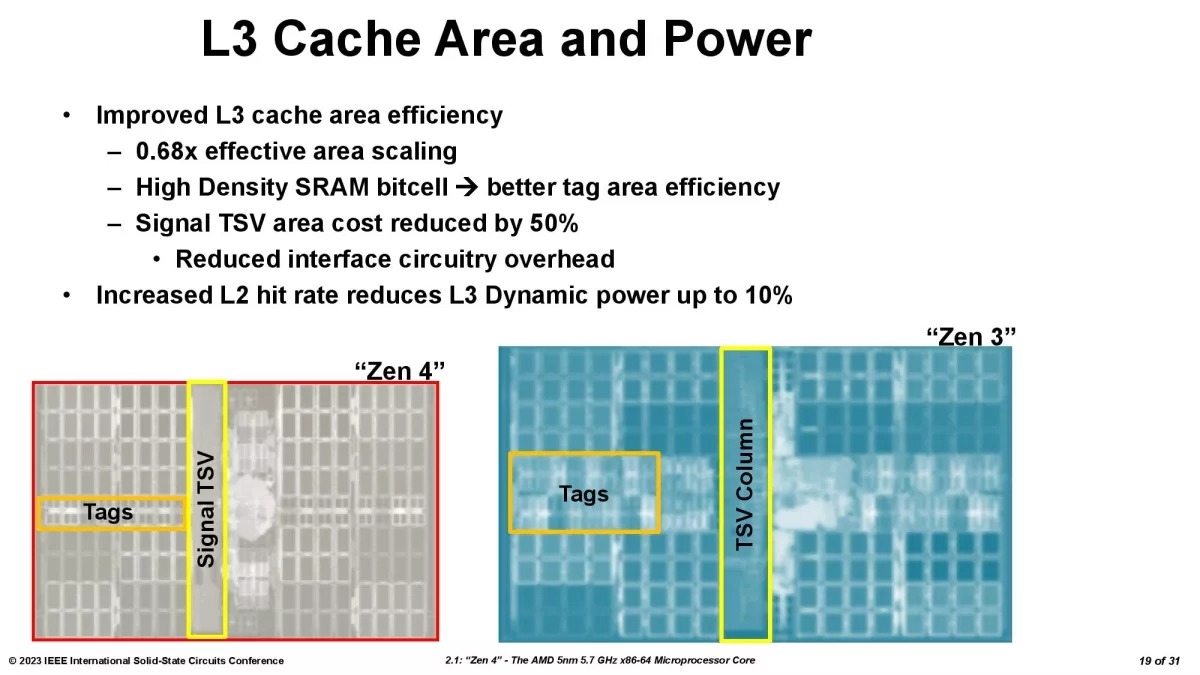

銳龍7000X3D上的容量還是64MB,工藝還是7nm,晶體管數量還是約47億個,但是面積縮小到36平方毫米,幅度約12%,密度因此增加到1.306億個/平方毫米。

這主要得益於更高密度的SRAM存儲單元,使得Ta標簽區域大大縮小,三級緩存的整體面積效率提升32%。

同時,TSV信號通道部分的成本降低50%,對接口電路的需求也大大減少。

順帶一提,5nm Zen4 CCD部分的面積為66.3平方毫米,晶體管65.7億個,密度9900萬個/平方毫米,7nm Zen3 CCD部分則是80.7平方毫米、41.5億晶體管、5140萬個/平方毫米,都不如3D緩存的集成度更高。

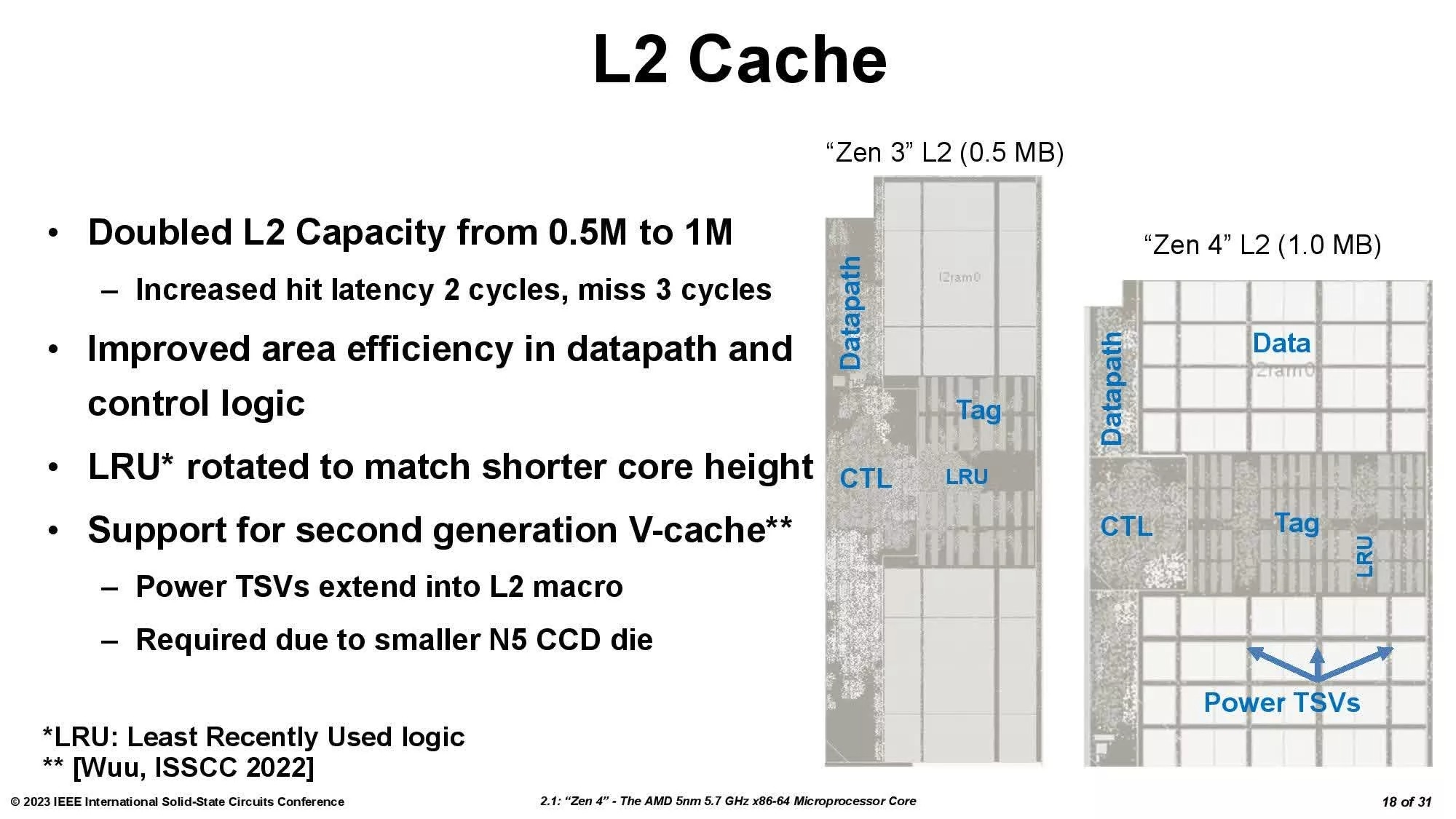

AMD還介紹Zen4二級緩存的更多細節,除大傢熟系的0.5MB容量翻番為1MB,還提升數據路徑和控制邏輯電路的集成度(面積更小),LRU(最近最少使用)單元旋轉90度以匹配更低的內核高度。

更關鍵的是,二級緩存部分可以和3D緩存相通,TSV供電通道直達二級緩存,這也是更小的5nm CCD所必需的。