JEDEC固態技術協會今天宣佈發佈JESD79-5CDDR5SDRAM標準。JEDECDDR5SDRAM標準的這一重要更新包括多項功能,旨在提高可靠性和安全性,並增強從高性能服務器到人工智能和機器學習等新興技術等廣泛應用中的性能。JESD79-5C規范文本現可從JEDEC網站下載。

JESD79-5C 引入一種創新的解決方案來改善 DRAM 數據完整性,即每行激活計數 (PRAC)。PRAC 在字行粒度上精確計算 DRAM 的激活次數。當支持 PRAC 的 DRAM 檢測到激活次數過多時,系統會發出警報,暫停流量並指定時間采取緩解措施。這些相互關聯的行動鞏固 PRAC 的能力,使其能夠通過 DRAM 與系統之間的密切協調,提供一種基本準確、可預測的方法來應對數據完整性挑戰。

JESD79-5C DDR5 提供的其他功能包括:

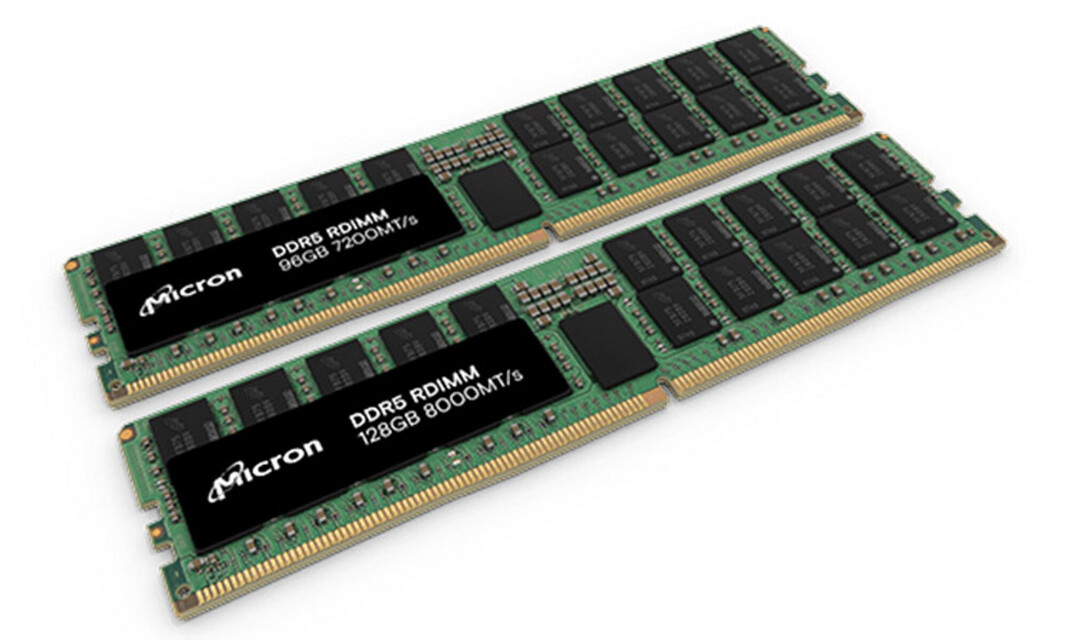

將定時參數定義從 6800 Mbps 擴展到 8800 Mbps

將 DRAM 內核定時和 Tx/Rx AC 定時擴展到 8800 Mbps,而之前的版本僅支持高達 6400 的定時參數和高達 7200 DRAM 內核定時的部分片段

引入自刷新退出時鐘同步,以優化 I/O 訓練

納入 DDP(雙芯片封裝)時序

棄用 PASR(部分陣列自刷新),以解決安全問題

JEDEC 董事會主席 Mian Quddus 說:"我很高興強調 JEDEC 的 JC-42 固態存儲器委員會為推進 DDR5 標準所做的共同努力。JESD79-5C中突破性的新功能旨在支持業界在廣泛應用中對安全性、可靠性和性能不斷發展的需求。"

"JC-42 委員會很高興推出 PRAC,這是一個有助於確保 DRAM 數據完整性的全面解決方案,是 DDR5 更新的一個組成部分。"JC-42 委員會主席 Christopher Cox 指出:"我們正在努力將這一功能納入 JEDEC 的其他 DRAM 產品系列。"