之前有說法稱,AMDZen5架構的單核理論性能相比Zen4可提升超過40%,相當不可思議,而根據MLID的最新說法,其中的秘密應該來自AVX-512指令集。AVX-512指令集原本是Intel的獨門秘籍,AMDZen4架構開始支持,包括消費級的銳龍、數據中心級的霄龍,而尷尬的是,Intel因為使用大小核架構設計,下一代的ArrowLake、LunarLake很大概率不再支持AVX-512(也沒有超

Zen4架構的AVX-512指令集是通過兩個256位FPU浮點單元來組合執行的,可以更靈活一些,功耗也更低,但性能達不到極致。

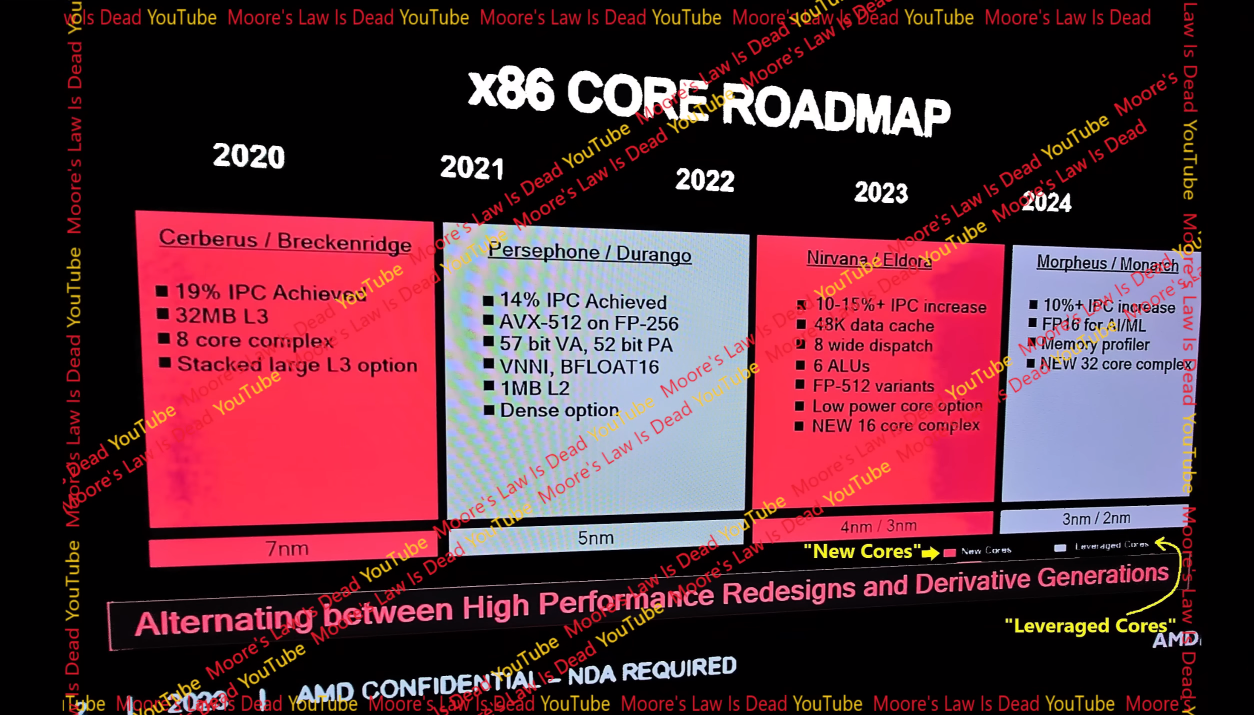

Zen5架構將會引入512位FPU單元,可以直接執行AVX-512,性能更強,也可高效執行VNNI等指令,更有利於提升AI表現。

為此,Zen5架構也會在其他方面升級配合,方便喂給FPU單元足夠的數據和指令。

比如增大一級緩存DTLB,一級數據緩存容量從32KB增大到48KB,比如載入存儲隊列加寬,比如FPU MADD延遲縮短一個時鐘周期,等等。

此外,Zen5架構的整數執行流水線也會從8條增加到10條。

不過,二級緩存容量保持不變,每核心還是1MB。