先進制程工藝進度緩慢的情況下,多芯片整合封裝成半導體行業的大趨勢,各傢不斷玩出新花樣。ISSCC2023國際固態電路大會上,AMD提出多種新的整合封裝設想,其中之一就是在CPU處理器內部,直接堆疊DRAM內存,而且是多層堆疊。

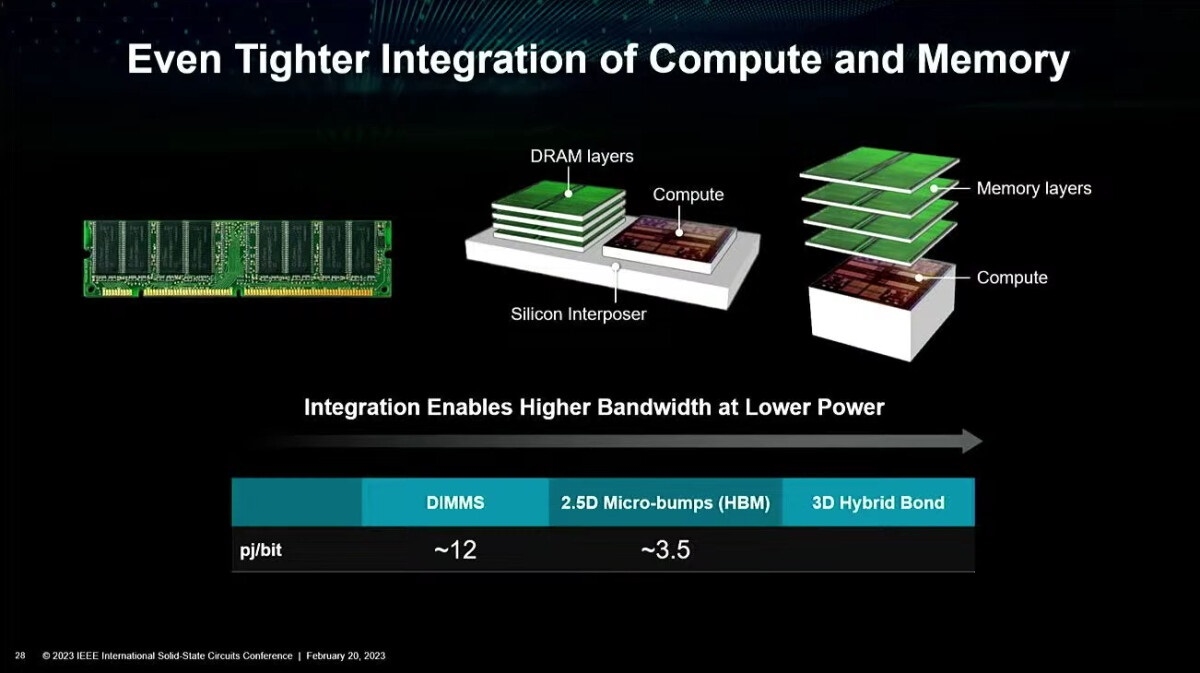

一種方式是CPU計算模塊、DRAM內存模塊,並排封裝在矽中介層上,而另一種方式就是在計算模塊上方直接堆疊內存模塊,有點像手機SoC。

AMD表示,這種設計可以讓計算核心以更短的距離、更高的帶寬、更低的延遲訪問內存,而且能大大降低功耗,2.5D封裝可以做到獨立內存功耗的30%左右,3D混合鍵合封裝更是僅有傳統的1/6。

如果堆疊內存容量足夠大,主板上的DIMM插槽甚至都可以省。

當然,AMD的這種設想僅面向服務器和數據中心領域,桌面上不會這麼做,否則就無法升級。

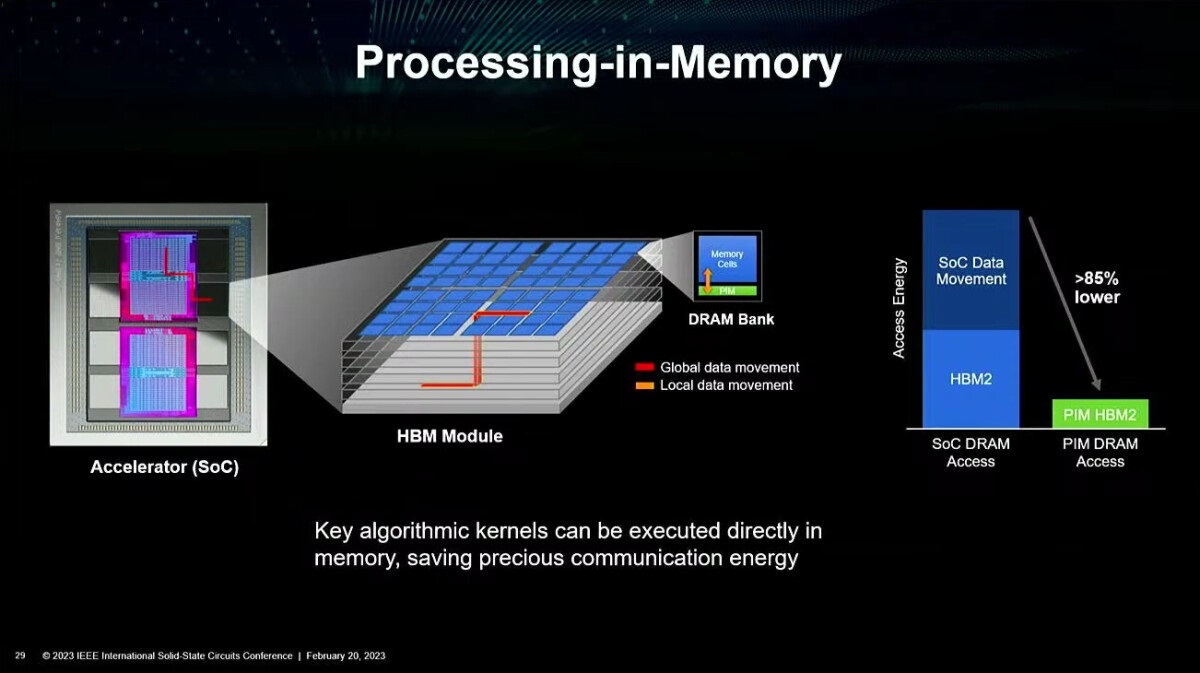

AMD甚至考慮在Instinct系列加速卡已經整合封裝HBM高帶寬內存的基礎上,在後者之上繼續堆疊DRAM內存,但隻是一層,容量不會太大。

這樣的最大好處是一些關鍵算法內核可以直接在整合內存內執行,而不必在CPU和獨立內存之間往復通信傳輸,從而提升性能、降低功耗。

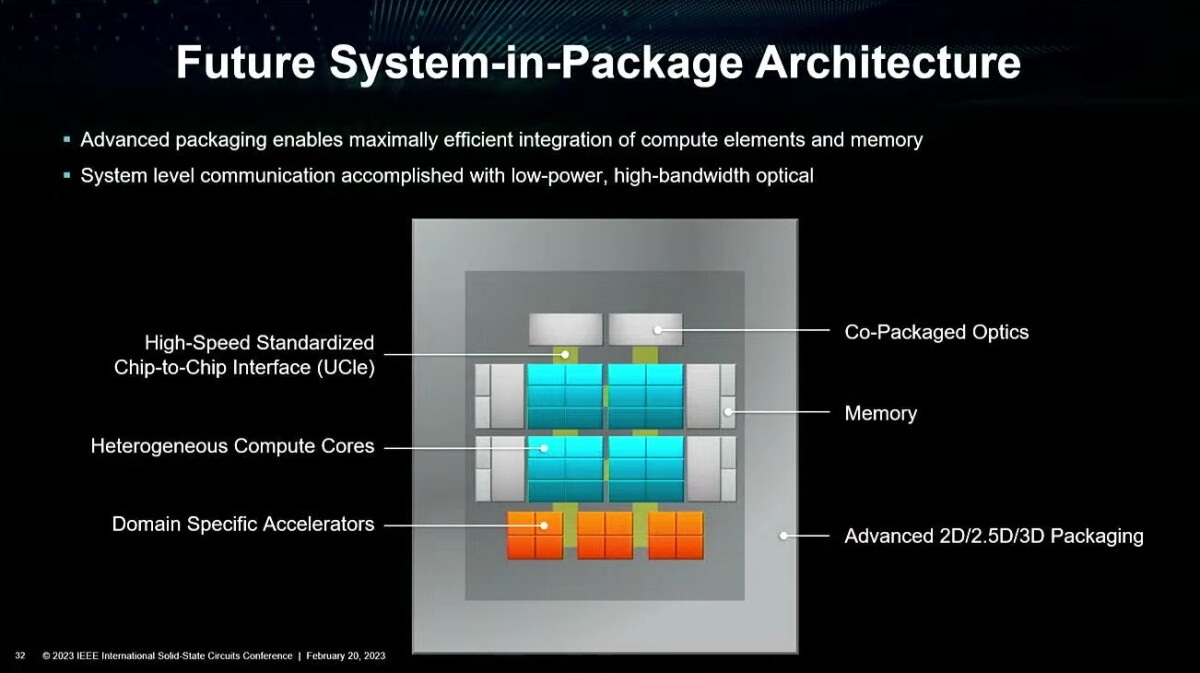

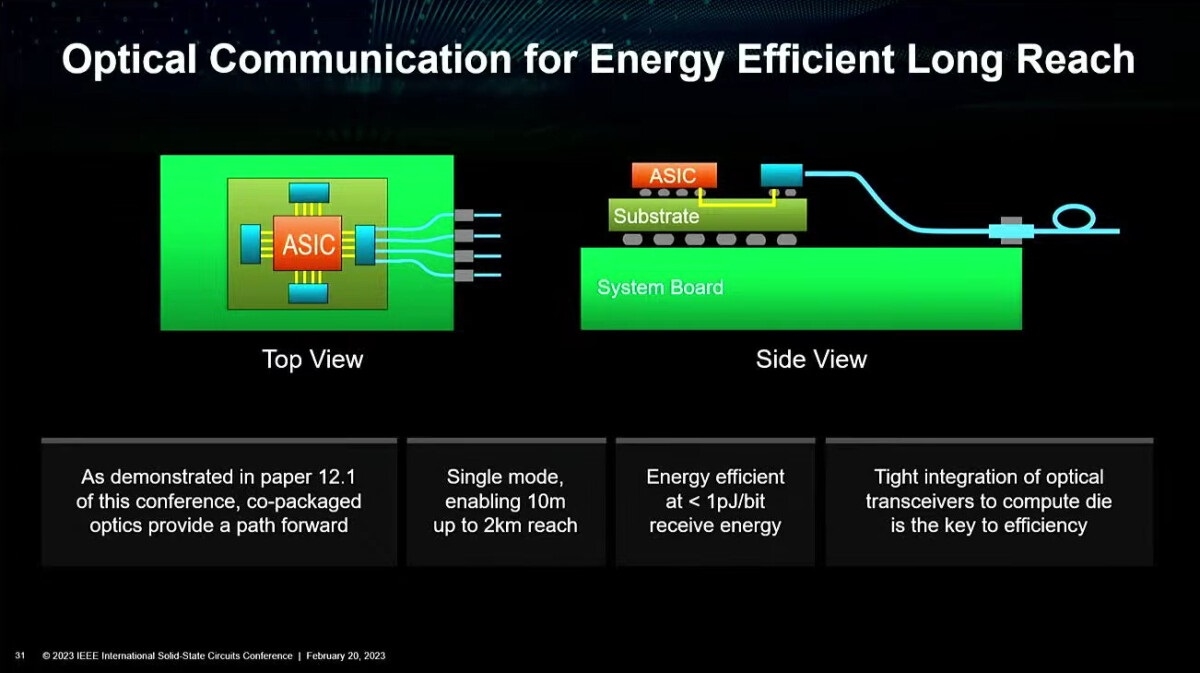

另外,AMD還設想在2D/2.5D/3D整合封裝芯片的內部,除CPU+GPU混合計算核心,還集成更多模塊,包括內存、統一封裝光網絡通道物理層、特定域加速器等等,並引入高速標準化的芯片間接口通道(UCIe)。

尤其是引入光網絡通道,可以大大簡化網絡基礎架構。