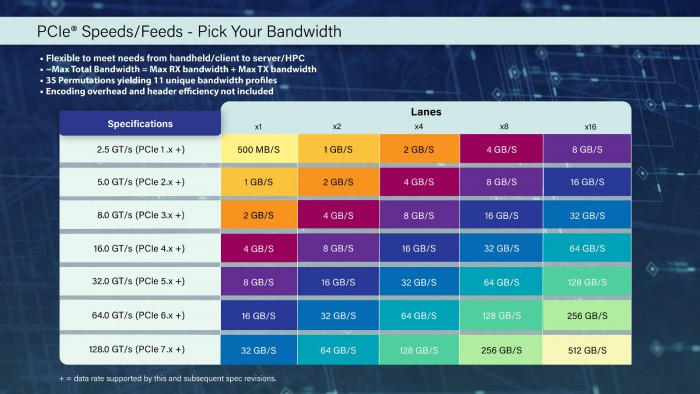

在完成瞭PCIe6.0的規范制定工作後,PCI-SIG又於本周二宣佈瞭PCIExpress7.0的新計劃。如果一切順利,新規范將於2025年正式推行。盡管目前PCIe5.0仍在普及階段,但放眼未來的PCIe7.0可支持128GT/s@x16的接口配置、以及高達512GB/s的雙向傳輸。

以下是 PCIe 7.0 規范的主要特點:

● 通過 x16 配置提供 128 GT/s 速率,以及 512 GB/s 雙向傳輸。

● 采用 PAM4 脈沖幅度調制信令

● 註重通道參數與范圍

● 進一步降低延遲與提升可靠性

● 改進能源效率

● 兼容以往所有 PCIe 版本

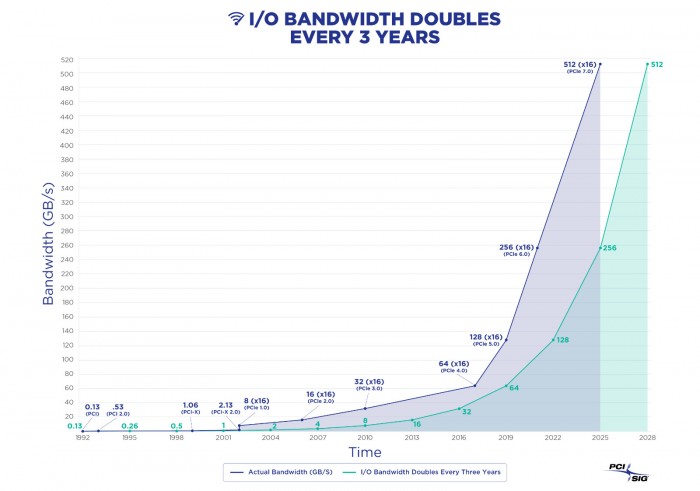

Insight 64 研究人員 Nathan Brookwood 表示:30 年來,PCI-SIG 時鐘貫徹著這樣的構建理念。

PCI 技術的早期並行版本,傳輸速率隻有數百 MB/s,這與 1990 年代的圖形、存儲和網絡需求相匹配。

2003 年的時候,PCI-SIG 推動瞭向支持數千 MB/s(數 GB/s)的串行設計轉型,以適應更高速的固態磁盤和以太網連接。

在上緊瞭發條之後,PCI-SIG 幾乎每隔三年就將 PCIe 規范帶寬提升一倍,以積極應對新興應用和市場的挑戰。

而今日新宣佈的 PCIe 7.0,更是將通道速度翻番到瞭雙向 512 GB/s,以延續在另一個三年周期內將 PCIe 規范性能提升一倍的目標。