PCI-SIG宣佈利用全新CopprLink電纜設計開發下一代PCIeGen5.0和Gen6.0標準。雖然PCI-SIG沒有詳細說明新CopprLink電纜的規格或設計變化,但它確認命名方案。CopprLink電纜將根據PCIeGen5.0和Gen6.0硬件提供內部和外部解決方案。根據PCI-SIG的說法,外部和內部電纜規格目前正在制定中,目標是在今年內發佈。以下是新聞稿全文:

PCI-SIG 在 SC23 大會上強調 PCIe 技術是高性能計算的首選互連技術,成員演示 PCIe 技術並宣佈新的 PCI Express 電纜命名方案。

PCI-SIG 宣佈 PCIe 內部和外部電纜的新命名方案為 CopprLink。PCIe 5.0 和 PCIe 6.0 內部和外部電纜規范目前正在開發中,預計將於 2024 年發佈。

PCI-SIG是擁有和管理作為開放式行業標準的PCI規范的聯盟,其成員將在SC23的1401號展位展示PCI Express (PCIe)技術演示。

PCI-SIG 邀請 SC23 參會者參觀 1401 號展臺,觀看演示並進一步解 PCIe 技術生態系統。演示將突出 PCIe 技術作為高性能計算 (HPC) 應用首選高速 I/O 互連技術的作用。參加演示的公司包括 Astera Labs、Dolphin Interconnect Solutions、Synopsys 和 Tektronix。

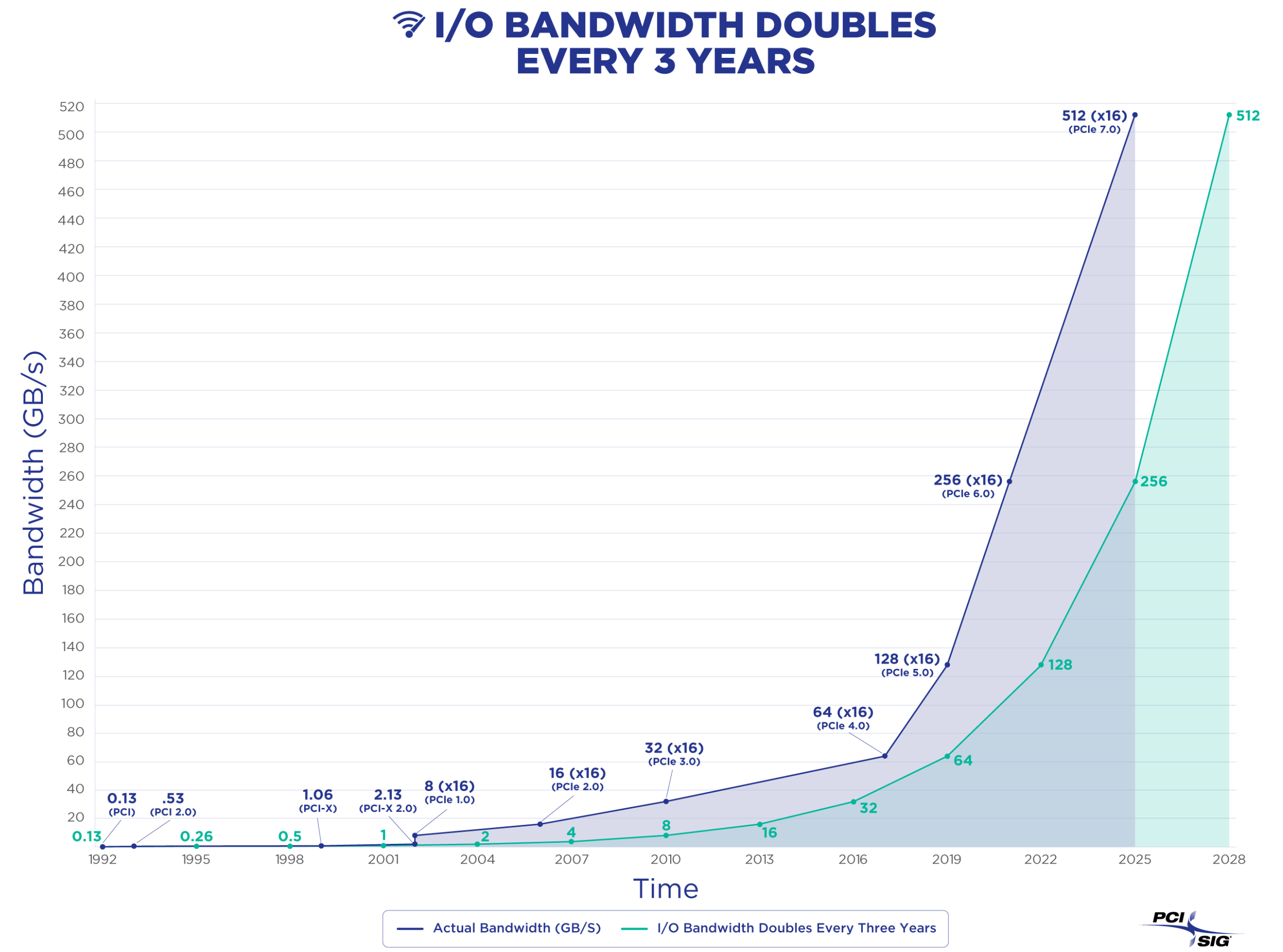

此次演示的重點是高性能計算應用,因此 CopprLink 應瞄準接口,我們可能會關註接口電纜而不是電源電纜,以便為下一代平臺上的各種設備提供最佳傳輸帶寬。PCIe 6.0 平臺的傳輸速率將翻一番,從 32 GT/s(5.0 代)提高到 64 GT/s(6.0 代)。新標準還有望在 x16 通道鏈路上提供 256 GB/s 的帶寬。

如果 CopprLink 與電源接口電纜有關,那麼PCI-SIG將努力解決在設計當前 12VHPWR Gen 5.0 標準時遇到的一些問題。雖然隨著 12V-2x6 標準的發佈,設計逐漸得到優化,但似乎仍有改進的餘地,尤其是考慮到未來的 PCIe Gen 6.0 硬件。期待在未來幾個月內解 CopprLink PCIe Gen 5.0 和 Gen 6.0 電纜的更多詳情。